Verilog

module pr_en ( input [7:0] a,

input [7:0] b,

input [7:0] c,

input [7:0] d,

input [1:0] sel,

output reg [7:0] out);

always @ (a or b or c or d or sel) begin

if (sel == 2'b00)

out <= a;

else if (sel == 2'b01)

out <= b;

else if (sel == 2'b10)

out <= c;

else

out <= d;

end

endmodule

module tb_4to1_mux;

reg [7:0] a;

reg [7:0] b;

reg [7:0] c;

reg [7:0] d;

wire [7:0] out;

reg [1:0] sel;

integer i;

pr_en pr_en0 ( .a (a),

.b (b),

.c (c),

.d (d),

.sel (sel),

.out (out));

initial begin

sel <= 0;

a <= $random;

b <= $random;

c <= $random;

d <= $random;

for (i = 1; i < 4; i=i+1) begin

#5 sel <= i;

end

#5 $finish;

end

endmodule

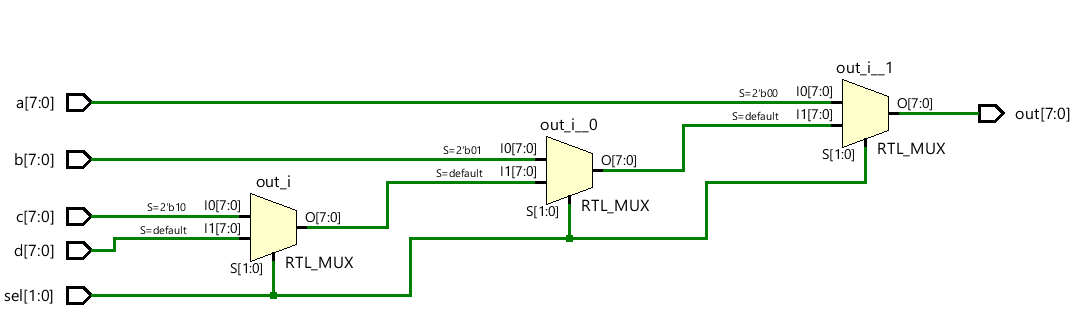

Verilog

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang

Desain module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else