Verilog

Desain

module johnson_ctr #(parameter WIDTH=4)

(

input clk,

input rstn,

output reg [WIDTH-1:0] out

);

always @ (posedge clk) begin

if (!rstn)

out <= 1;

else begin

out[WIDTH-1] <= ~out[0];

for (int i = 0; i < WIDTH-1; i=i+1) begin

out[i] <= out[i+1];

end

end

end

endmodule

Testbench

Log Simulasi

module tb;

parameter WIDTH = 4;

reg clk;

reg rstn;

wire [WIDTH-1:0] out;

johnson_ctr u0 (.clk (clk),

.rstn (rstn),

.out (out));

always #10 clk = ~clk;

initial begin

{clk, rstn} <= 0;

$monitor ("T=%0t out=%b", $time, out);

repeat (2) @(posedge clk);

rstn <= 1;

repeat (15) @(posedge clk);

$finish;

end

endmodule

ncsim> run

T=0 out=xxxx

T=10 out=0001

T=50 out=0000

T=70 out=1000

T=90 out=1100

T=110 out=1110

T=130 out=1111

T=150 out=0111

T=170 out=0011

T=190 out=0001

T=210 out=0000

T=230 out=1000

T=250 out=1100

T=270 out=1110

T=290 out=1111

T=310 out=0111

Simulation complete via $finish(1) at time 330 NS + 0

Verilog

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang

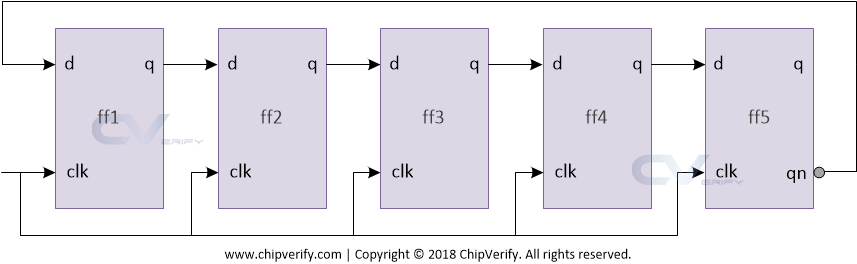

riak pencacah adalah pencacah asinkron di mana semua flop kecuali yang pertama di-clock oleh output dari flop sebelumnya. Desain module dff ( input d, input clk, input rstn, output reg q, output qn); always @ (posedge clk or neg

Desain module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+1) b