Desain dan Penelitian PCB tentang Kartu Sandi Berkecepatan Tinggi Berdasarkan PCIE

Saat ini, perkembangan teknologi internet yang pesat menyaksikan aplikasi email, pembayaran online, dan komunikasi pribadi yang masif. Di bawah latar belakang ini, keamanan informasi telah menjadi tema penelitian penting di seluruh dunia. Teknologi PKI (Public Key Infrastructure) menyediakan layanan keamanan dengan menggunakan teori dan teknologi kunci publik. Teknologi PCIE (Peripheral Component Interface Express) telah menerima aplikasi luas pada perangkat berkecepatan tinggi sebagai standar bus I/O generasi ketiga yang menerapkan transmisi data serial dan teknologi interkoneksi titik-ke-titik. Di bidang desain sistem digital, frekuensi clock yang relatif tinggi menyebabkan beberapa masalah dalam perspektif integritas sinyal, integritas daya dan crosstalk dan desain PCB tradisional gagal memenuhi persyaratan stabilitas sistem.

Artikel ini menawarkan skema desain PCB pada kartu sandi berkecepatan tinggi berdasarkan PCIE sesuai dengan manfaat transmisi serial berkecepatan tinggi PCIE.

Skema Desain Keseluruhan

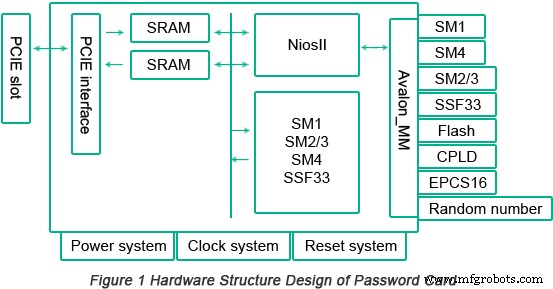

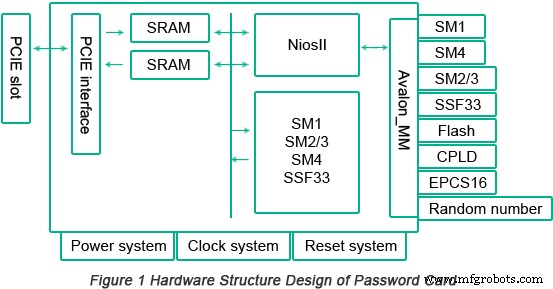

Chip FPGA EP4CGX50CF23C6N milik Cyclone IV GX yang dirancang oleh Altera diterapkan dalam desain ini, mengintegrasikan modul hardcore PCIE IP dan menerapkan 4 desain kartu kata sandi transmisi data berkecepatan tinggi. Empat jenis chip, chip 1, chip 2, chip 3 dan chip 4, masing-masing mampu mengimplementasikan algoritma SM1, SM2/SM3, SM4 dan SSF33 dan mengimplementasikan fungsionalitas inisialisasi kartu kata sandi, administrasi kunci rahasia, pencadangan dan pemulihan, serta otoritas pengelolaan. Kartu kata sandi diterapkan di PC, terhubung dengan papan utama di PC melalui slot PCIE dan dikendalikan oleh PC. IP hardcore di FPGA diterapkan untuk mengimplementasikan PCIE, yang mengarah ke komunikasi antara inti PCIE dan cache SRAM dan modul kontrol. Sebagai pusat kendali, NiosII mengimplementasikan fungsi perangkat lunak kartu kata sandi. Sementara itu, chip kata sandi tambahan mengimplementasikan komunikasi antara setiap modul antarmuka dan kartu kata sandi. Desain struktur perangkat keras kartu sandi diilustrasikan pada Gambar 1 di bawah ini.

Desain PCB Berkecepatan Tinggi

• Penumpukan dan tata letak

Desain tumpukan adalah masalah paling signifikan yang harus diperhitungkan dan desain tumpukan yang wajar dapat menghambat radiasi EMI (Elcetromagnetic Interference), membuat tegangan transien pada bidang daya atau lapisan tanah menjadi sekecil mungkin dan melindungi medan elektromagnetik dari sinyal dan daya. Umumnya, papan multi-layer dan beberapa kekuatan diterapkan dalam desain sirkuit digital berkecepatan tinggi. Desain susun PCB diimplementasikan berdasarkan elemen komprehensif termasuk frekuensi jam sirkuit, biaya fabrikasi PCB, kepadatan pin, periode manufaktur, dan keandalan. Selain itu, lapisan papan multi-layer harus dijaga simetris dan jumlah papan harus genap karena desain susun yang tidak simetris akan menyebabkan papan melengkung. Kartu kata sandi yang dirancang dalam artikel ini terhubung dengan PC melalui slot PCIE dan ukuran serta bentuk papan sirkuit ditetapkan dengan tinggi sekitar 67mm dan panjang sekitar 174mm, mengkonfigurasi pin antarmuka PCIE X4 di bagian bawah. Sebagai hasil dari kepadatan komponen yang tinggi dan perutean yang tebal, jumlah lapisan PCB diambil sebagai 6 lapisan dengan distribusi lapisan sinyal, lapisan daya, lapisan sinyal, lapisan daya, lapisan tanah, lapisan sinyal. Desain ini berisi 3 lapisan sinyal, 1 lapisan tanah dan 2 lapisan daya, menyediakan lingkungan yang dibutuhkan oleh integritas sinyal.

Setelah penentuan susunan PCB, kelompok komponen dan tata letak harus diterapkan. Pertama, posisi komponen harus diprogram sesuai dengan dimensi dan pola PCB, dengan mempertimbangkan sambungan jalur, partisi fungsional, trim, dan keindahan antar komponen. Kemudian, komponen harus didistribusikan secara wajar menurut tingkat tegangan komponen yang berbeda untuk membuat kabel tegangan sependek mungkin, yang mampu mengurangi gangguan kebisingan daya dan meningkatkan stabilitas daya. Penempatan chip harus memperhatikan hubungan antara sirkuit bantu dan chipnya dan penempatan osilator kristal di belakang pin jam. Komponen kebisingan tinggi harus dihindari ditempatkan di sekitar osilator kristal dan harus berada di dekat komponen penggeraknya. Selanjutnya, penempatan masing-masing chip power dan pin sinyal harus diperhatikan dengan posisi dan arah yang disesuaikan berdasarkan jalur yang terhubung. Karena rasio panjang dan lebar kartu sandi lebih dari 2:1 dengan posisi slot PCIE, lubang pemuatan dan LED penunjuk tetap, tata letak komponen untuk komponen tetap harus dipertimbangkan terlebih dahulu dalam tata letak komponen. Selain itu, karena banyaknya jalur penghubung antara komponen dan FPGA, tata letak komponen harus diterapkan dengan FPGA sebagai pusat sebelum penempatan komponen lain sehingga ruang atas dan bawah PCB dapat digunakan secara efektif agar untuk menyisakan ruang yang cukup antara komponen dan komponen serta lubang pemosisian.

• Desain daya

Dalam desain papan sirkuit berkecepatan tinggi, desain sistem tenaga berhubungan langsung dengan keberhasilan keseluruhan sistem. Kebisingan yang dihasilkan oleh daya dan tanah harus dikurangi seminimal mungkin untuk memastikan keandalan produk. Penerapan skema distribusi daya dalam metode lapisan mengacu pada kenyataan bahwa daya didistribusikan melalui logam di seluruh lapisan, mengurangi impedansi daya dan kebisingan dan meningkatkan keandalan. Karena beberapa kekuatan diperhatikan oleh PCB, desain lapisan multi-daya harus diterapkan, yang mampu menghilangkan gangguan kopling impedansi publik sebagai loop kebisingan. Penerapan kapasitansi decoupling mampu memecahkan masalah integritas daya karena kapasitor hanya dapat ditempatkan pada lapisan bawah atau lapisan atas PCB, berdasarkan kabel yang menghubungkan kapasitor decoupling harus pendek dan lebar. Menurut bahan chip, arus yang melewati saluran listrik dapat dihitung dan lebar kabel dapat ditentukan. Semakin lebar sadapannya, semakin banyak arus yang dapat dibawanya. Rumus eksperimen diilustrasikan sebagai:W(lebar garis:mm) L(mm/A) x I(arus:A)

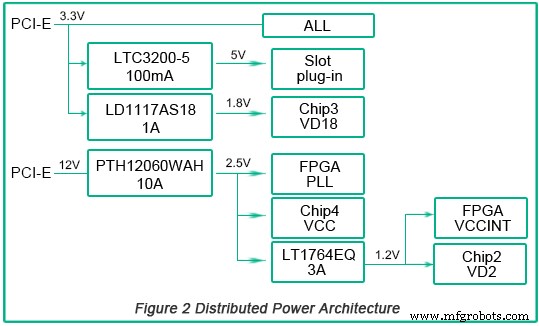

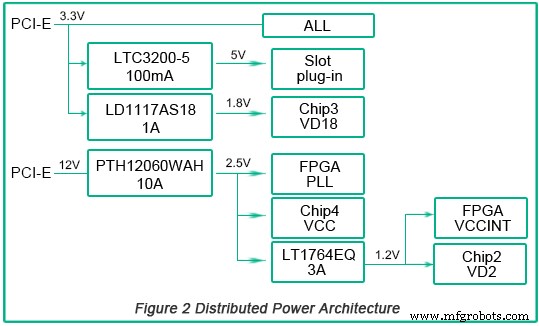

Beberapa daya pada PCB memperoleh satu atau dua jenis daya dari papan daya menggunakan papan belakang dan daya tersebut kemudian diubah menjadi daya lain yang diperlukan oleh komponen. Konversi daya dibagi menjadi dua arsitektur:arsitektur daya terpusat dan arsitektur daya terdistribusi. Yang pertama mengacu pada daya yang dipasok oleh daya independen dan kemudian diubah menjadi semua jenis daya yang diperlukan, sedangkan yang kedua mengacu pada konversi daya multi-tingkat. Karena arsitektur daya terpusat memiliki kelemahan biaya tinggi dan area PCB besar, arsitektur daya terdistribusi diterapkan dalam desain ini. Kartu kriptografi menyangkut 6 kekuatan, termasuk 12V, 3.3V, 5V, 2.5V, 1.2V dan 1.8V. Perancangan ini dimulai dengan penyertaan daya 3.3V dan 12V di slot PCIE dan kemudian daya 3.3V mampu menghasilkan daya 5V dan daya 1.8V melalui chip konversi tegangan, memasok daya untuk plug-in dan chip 3. Selanjutnya, daya 12V adalah diubah menjadi daya 2.5V untuk memasok daya untuk FPGA dan chip 4. Terakhir, daya 2.5V diubah menjadi daya 1.2V untuk memasok daya untuk FPGA dan chip 2. Arsitektur daya terdistribusi dari kartu kriptografi ditunjukkan pada Gambar 2 di bawah.

• Desain lubang tembus

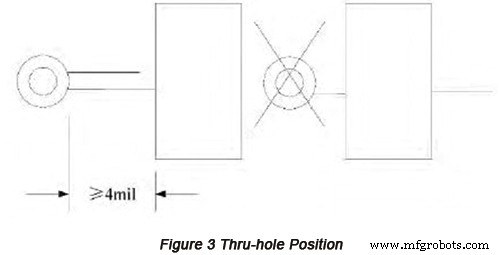

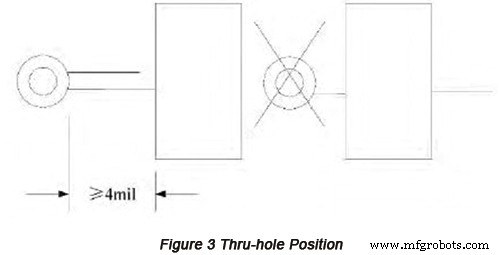

Dalam proses tata letak desain untuk PCB multi-layer dengan kepadatan tinggi, melalui lubang harus diterapkan, mentransmisikan sinyal dari satu lapisan ke lapisan lain untuk menyediakan komunikasi listrik antar lapisan. Desain posisi lubang tembus harus dilaksanakan dengan sangat hati-hati. Lubang tembus tidak boleh ditempatkan pada bantalan dan satu garis cetak dapat diterapkan untuk sambungan, jika tidak menyebabkan masalah seperti batu nisan dan solder yang tidak mencukupi. Soldermask harus dilapisi melalui lubang pad dengan jarak yang diatur menjadi 4 mil dan lubang tembus tidak boleh ditempatkan di tengah pad untuk komponen chip di sisi solder. Posisi lubang-lubang diilustrasikan pada Gambar 3 di bawah ini.

Selain itu, posisi lubang tidak boleh terlalu dekat dengan jari emas yang sisi plug-innya harus berisi talang. Untuk membuat papan sirkuit terpasang di slot PCIE, talang (1~1.5)x45° dapat dirancang pada dua sisi sisi papan plug-in.

• Perutean sinyal berkecepatan tinggi

Dalam proses perutean, distribusi harus disesuaikan secara wajar untuk membuat jalur penghubung seminimal mungkin sehingga crosstalk dapat dikurangi. Dalam proses perutean sinyal digital berkecepatan tinggi, lapisan sinyal di dekat perutean lapisan multi-daya harus jauh dari permukaan referensi daya untuk menghindari pembentukan jalur kembali oleh arus sinyal.

Karena frekuensi sinyal jam sirkuit berkecepatan tinggi relatif tinggi, jitter, drifting dan deformasi sangat mempengaruhi sistem sehingga desain PCB berkecepatan tinggi memerlukan gangguan gelombang sinyal kecil. Oleh karena itu, masalah distribusi jam dan perutean harus dipertimbangkan terlebih dahulu. Perutean harus diterapkan pada sinyal clock berkecepatan tinggi dan perutean jalur sinyal clock utama harus sesingkat mungkin, lurus dan bebas dari lubang-lubang dan bagian daya untuk mencegah crosstalk antara jam dan daya. Ketika beberapa jam dengan frekuensi yang berbeda diterapkan pada PCB yang sama, dua garis jam dengan frekuensi yang berbeda tidak boleh dipertahankan paralel. Namun, untuk beberapa komponen yang menggunakan sinyal clock dengan frekuensi yang sama, jaringan dapat didistribusikan berdasarkan jenis laba-laba, jenis pohon, dan jenis cabang.

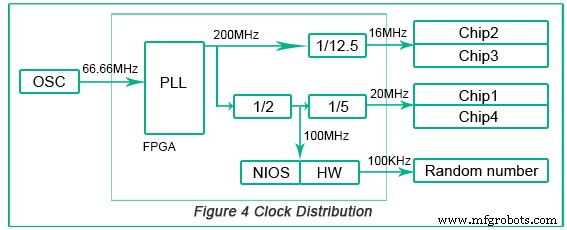

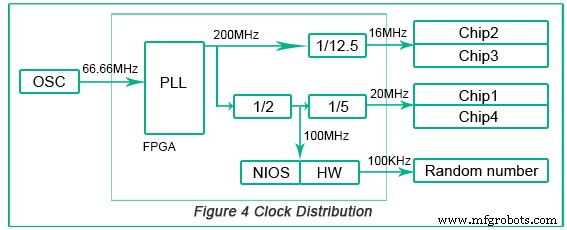

Dalam kartu kriptografi berkecepatan tinggi, FPGA memperoleh clock 66.66MHz melalui osilator kristal pada PCB. Setelah looping dengan kunci intrinsik di dalam FPGA, jam dasar 200MHz dihasilkan sebagai antarmuka untuk chip 2 dan chip 3 untuk mengoperasikan jam. Kemudian jam 100MHz disediakan setelah rangkaian pembagi frekuensi intrinsik sebagai softcore NiosII dan jam kerja rangkaian perangkat keras di dalam FPGA. Frekuensi terbagi 16MHz adalah jam kerja chip 2 dan chip 3 sedangkan frekuensi terbagi 20MHz adalah jam kerja chip 1 dan chip 4. Distribusi clock ditampilkan pada Gambar 4 di bawah ini.

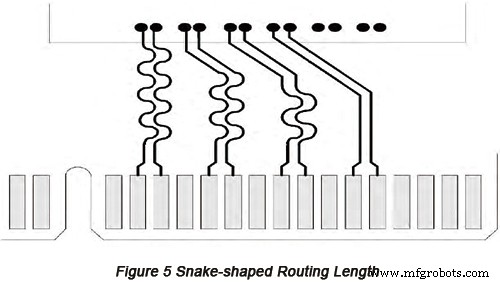

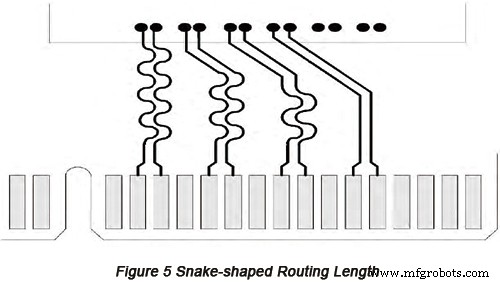

Transmisi sinyal berkecepatan tinggi antara slot PCIE dan PC diimplementasikan oleh kartu kriptografi berkecepatan tinggi dalam cara perutean pasangan diferensial untuk menghindari masalah terkait integritas sinyal. Secara umum, kabel pembumian tidak ditempatkan di antara sinyal pasangan diferensial, jika tidak, efek kopling antara sinyal pasangan diferensial akan dihancurkan. Setelah perutean sinyal pasangan diferensial, tembaga ditempatkan di sekitar sinyal kecepatan tinggi PCB dengan ruang kosong yang terisi penuh dengan kabel arde untuk meningkatkan kemampuan EMI sirkuit. Kunci dari perutean PCB adalah menjaga simetri pasangan diferensial. Jika panjang pasangan diferensial tidak kompatibel, akurasi pembacaan dan penulisan data akan terpengaruh dengan penurunan kecepatan transmisi data. Untuk memastikan validitas sistem pembacaan data dalam periode yang sama, perbedaan penundaan antara sinyal diferensial harus dipertahankan dalam kategori yang diizinkan dan panjang perutean harus benar-benar sama. Oleh karena itu, routing berbentuk ular dapat diterapkan untuk mengatasi masalah ini dengan mengatur waktu tunda. Dalam desain ini, komunikasi diimplementasikan oleh PC melalui PCIE dan kartu kriptografi dan transmisi dan penerimaan sinyal berkecepatan tinggi diimplementasikan oleh sinyal pasangan diferensial dengan panjang perutean PCB yang dikontrol dalam 25mil. Diagram pencocokan panjang perutean berbentuk ular diilustrasikan pada Gambar 5.

Sumber Daya Bermanfaat

• Bagaimana Mendesain PCB Berkualitas Tinggi

• Elemen Desain PCB yang Mempengaruhi Manufaktur SMT

• Penelitian Desain PCB Berkecepatan Tinggi dalam Sistem Aplikasi Tertanam

• Pemrosesan Isometrik Diferensial dan Verifikasi Simulasi Desain PCB Berkecepatan Tinggi

• Layanan Pembuatan PCB Fitur Lengkap dari PCBCart - Beberapa opsi Nilai tambah

• Layanan Perakitan PCB Tingkat Lanjut dari PCBCart - Mulai dari 1 buah