Cara Menganalisis dan Melarang Impedansi Daya PCB Berkecepatan Tinggi

Dengan meningkatnya kompleksitas desain PCB, catu daya yang stabil dan andal telah menjadi tren baru penelitian desain PCB berkecepatan tinggi. Terutama ketika jumlah komponen switching terus meningkat dan Vcore terus menurun, fluktuasi daya cenderung membawa pengaruh yang mematikan pada sistem. Oleh karena itu, ini telah menjadi titik kunci dalam desain PCB berkecepatan tinggi untuk menjaga stabilitas sistem tenaga.

Namun, akibat adanya impedansi sistem tenaga, jatuh tegangan yang relatif besar dihasilkan oleh arus transien beban pada impedansi sistem tenaga, yang menyebabkan ketidakstabilan sistem. Untuk memastikan bahwa daya normal disuplai ke setiap komponen dari awal hingga akhir, impedansi dalam sistem tenaga harus dikontrol, yang berarti bahwa impedansi harus dikurangi sebanyak mungkin.

Penerapan kapasitor decoupling merupakan cara yang efektif untuk mencegah impedansi pada sistem tenaga listrik. Artikel ini menganalisis alasan larangan impedansi dalam sistem tenaga dengan decoupling kapasitor dan daftar metode dalam hal pemilihan kapasitor decoupling. Selain itu, penelitian ini terutama tentang bagaimana menentukan posisi decoupling kapasitor berdasarkan analisis harmonik untuk memaksimalkan larangan impedansi dalam sistem tenaga.

Analisis Impedansi

Daya dan ground dapat dianggap sebagai kapasitor pelat besar yang kapasitasnya dihitung berdasarkan rumus C=kAr/d

Dalam rumus ini, k adalah 0,2249 inci; A mengacu pada area paralel antara dua bidang; r mengacu pada konstanta dielektrik medium dan 4,5 untuk bahan papan FR4 yang umum digunakan; d mengacu pada jarak antara daya dan tanah. Sebuah PCB dengan ukuran 2x1 inci diambil sebagai contoh. Kapasitansi kapasitor yang dibentuk oleh daya dan tanah dengan luas paralel 20Mils adalah sekitar 0.2249x4.5x2x1/0.02=101.2pF. Berdasarkan rumus ini, dapat ditunjukkan bahwa kapasitansi decoupling dalam sistem tenaga sangat kecil sehingga impedansi yang sesuai akan sangat besar, umumnya beberapa ohm. Oleh karena itu, jauh dari cukup untuk mengurangi impedansi melalui self-decoupling dalam sistem tenaga.

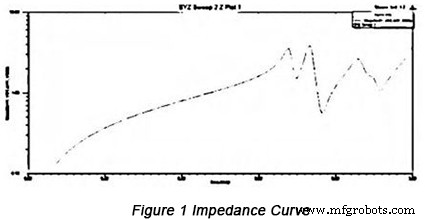

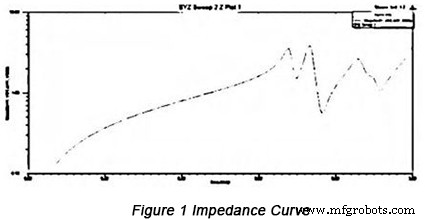

Alat simulasi SIWAVE pada level 2.5D diterapkan untuk mengimplementasikan simulasi impedansi pada perangkat aktif. Jaringan daya dan ground U41 diambil untuk menghitung parameter XYZ dengan rentang sapuan dari 0 hingga 1GHz, yang melaluinya kurva impedansi diperoleh pada Gambar 1 di bawah ini.

Pada diagram terlihat bahwa kurva impedansi berubah dengan perubahan frekuensi dan perubahan impedansi sangat besar pada titik belok pada nilai 670MHz, 730MHz dan 870MHz.

Metode Larangan

• Analisis teoritis tentang larangan impedansi dengan decoupling kapasitor

Karena tidak mungkin untuk mengurangi impedansi melalui decoupling dari daya itu sendiri, kapasitor decoupling harus diterapkan untuk mencegah impedansi.

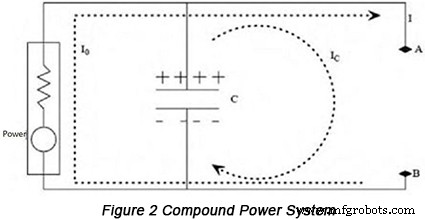

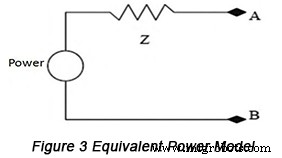

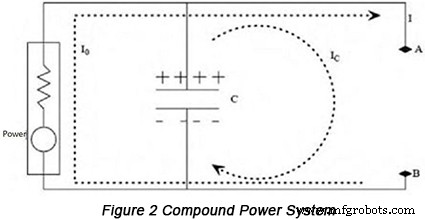

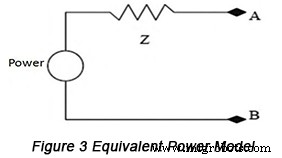

Gambar 2 adalah diagram sistem tenaga majemuk. Gambar 3 menunjukkan sistem daya ini dalam model daya yang setara.

Rumus dapat diterapkan untuk mewakili rangkaian ini:V=ZxL. Suatu keadaan harus dicapai bahwa bahkan jika arus transien beban mempertahankan perubahan besar antara titik A dan titik B, perubahan tegangan harus sangat kecil antara dua titik. Berdasarkan rumus, tujuan ini tidak akan pernah diperoleh kecuali nilai impedansi (Z) cukup kecil. Pada Gambar 3, penerapan decoupling kapasitor sangat membantu untuk pelaksanaan tujuan ini sehingga dapat ditunjukkan bahwa kapasitor decoupling mampu menurunkan impedansi dalam sistem tenaga dari perspektif ekivalensi. Selanjutnya, dari perspektif prinsip sirkuit, kesimpulan yang sama dapat dipertahankan. Kapasitor memiliki impedansi rendah pada sinyal arus bolak-balik. Akibatnya, partisipasi kapasitor sebenarnya pasti akan mengurangi impedansi arus bolak-balik dalam sistem tenaga.

• Pemilihan kapasitansi kapasitor decoupling

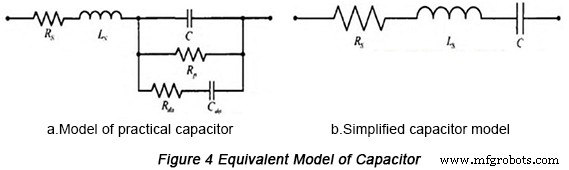

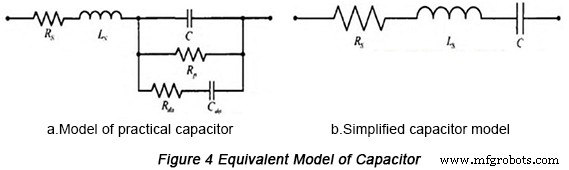

Tidak pernah ada kapasitor yang ideal, selalu memiliki parameter parasit. Pengaruh terbesar pada kinerja frekuensi tinggi kapasitor berasal dari ESR (Effective Series Inductance) dan ESL (Effective Series Resistance). Gambar 4 menunjukkan model ekivalen dengan pertimbangan parameter parasit.

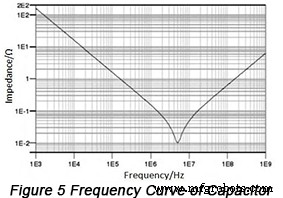

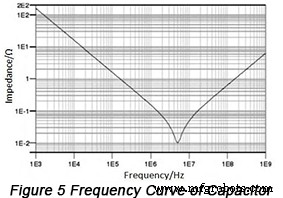

Kapasitor dapat juga dianggap sebagai rangkaian harmonik seri dengan frekuensi harmonik seri mengikuti rumus:f=1/2PIFC. Ketika tetap dalam keadaan frekuensi rendah, ini menampilkan kapasitansi. Namun, ketika frekuensi naik, ia terus-menerus menampilkan induktansinya. Dengan kata lain, impedansinya akan naik terlebih dahulu kemudian menyusut dengan meningkatnya frekuensi dan nilai minimum impedansi ekivalen terjadi pada frekuensi harmonik seri f0 . Pada saat ini, reaktansi kapasitif dan reaktansi induktif diimbangi dengan benar, menampilkan kesetaraan antara nilai impedansi dan ESR dengan resistansi setara kapasitor terkecil. Kurva frekuensi kapasitor ditunjukkan pada Gambar 5.

Oleh karena itu, dalam proses pemilihan kapasitor, titik frekuensi harmonik kapasitor yang dipilih berada berdekatan dengan titik frekuensi yang akan mengalami decoupling. Kinerja kapasitifnya harus sepenuhnya diterapkan dan digunakan sebelum frekuensi harmonik sendiri bila memungkinkan.

Kapasitor yang berbeda dengan kapasitansi yang berbeda kompatibel dengan frekuensi harmonik diri yang berbeda ditampilkan pada tabel di bawah ini.

| Kapasitas | DIP (MHz) | STM (MHz) |

| 1.0μF | 2.5 | 5 |

| 0.1μF | 8 | 16 |

| 0.01μF | 25 | 50 |

| 1000pF | 80 | 160 |

| 100pF | 250 | 500 |

| 10pF | 800 | 1,6(GHz) |

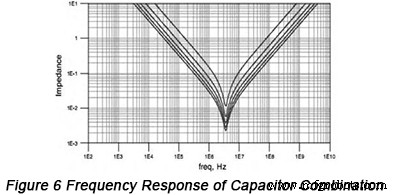

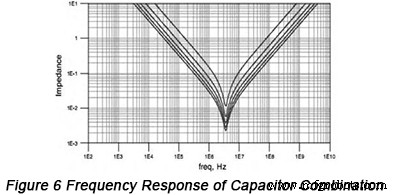

Umumnya, sifat harmonik kapasitor decoupling diperlukan untuk diterapkan dan impedansi input terendah diperoleh melalui kombinasi paralel kapasitor. Respon frekuensi paralel dari jenis kapasitor yang sama diilustrasikan pada Gambar 6 di bawah ini.

Berdasarkan metode ini, ESR dan ESL yang setara dapat sangat dikurangi. Untuk beberapa kapasitor (n) dengan kapasitansi yang sama, kapasitansi ekivalen C menjadi nC setelah kombinasi sedangkan induktansi ekivalen L menjadi L/n, ESR ekivalen menjadi R/n. Namun, frekuensi harmonik tetap tidak berubah. Dapat dilihat bahwa karena frekuensi harmonik sendiri sama untuk jenis kapasitor yang berbeda, semakin banyak kapasitor paralel, semakin kecil impedansi di daerah kapasitif dan induktif, dengan titik frekuensi harmonik sendiri tidak berubah.

Kesimpulannya, dalam proses pemilihan kapasitor decoupling, frekuensi decoupling harus dianggap sebagai titik frekuensi harmonik diri decoupling sehingga kapasitor yang sesuai dapat diambil. Selain itu, penerapan paralel beberapa kapasitor dengan kapasitansi yang sama mampu meningkatkan kapasitas decoupling dan mengurangi impedansi.

• Penentuan posisi kapasitor decoupling

Setelah pemilihan kapasitor decoupling, posisinya harus diperhitungkan. Daya dan bidang tanah dapat dianggap sebagai jaringan yang disusun oleh beberapa induktor dan kapasitor atau rongga resonansi. Pada frekuensi tertentu, resonansi terjadi pada induktor dan kapasitor, mempengaruhi impedansi dalam sistem tenaga. Dengan peningkatan frekuensi, impedansi berubah secara konstan terutama ketika resonansi paralel tetap luar biasa, impedansi juga meningkat secara luar biasa. Oleh karena itu, posisi spesifik kapasitor decoupling harus dipastikan digabungkan dengan analisis harmonik PCB.

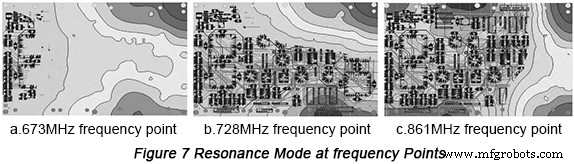

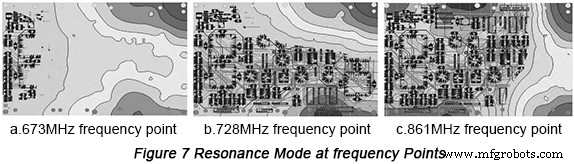

Dengan fungsi analisis resonansi alat simulasi SIWAVE yang diterapkan, parameter ekivalen dipimpin termasuk resistansi, kapasitansi, dan induktansi. Selain itu, analisis resonansi PCB harus diimplementasikan dengan mode resonansi pada titik frekuensi berbeda yang diperoleh, seperti yang ditunjukkan pada Gambar 7.

Digabungkan dengan Gambar 1, dapat diamati bahwa beberapa titik frekuensi dengan impedansi yang relatif besar kompatibel dengan titik frekuensi di mana resonansi dihasilkan. Oleh karena itu, dengan hasil analisis resonansi, dapat disimpulkan bahwa di daerah dengan kapasitor decoupling resonansi yang serius dengan kapasitansi yang sesuai harus ditempatkan untuk mengurangi impedansi.

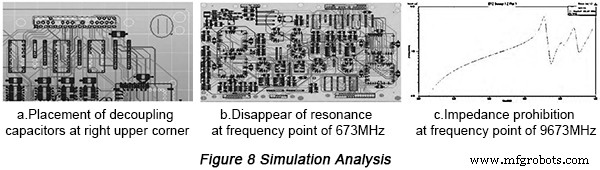

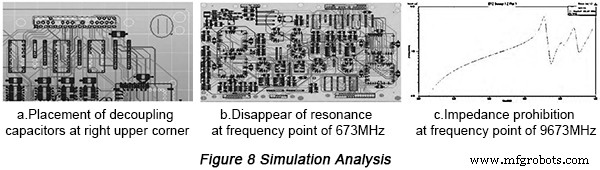

Ambil titik frekuensi 673MHz sebagai contoh, kapasitor decoupling dapat ditempatkan secara paralel sehingga resonansi akan ditemukan hilang dan impedansi yang sesuai akan dilarang, seperti yang ditunjukkan pada Gambar 8.

Berdasarkan analisis resonansi PCB, posisi yang sesuai di mana resonansi terjadi dapat ditentukan, berdasarkan kapasitor dengan ukuran yang sesuai ditempatkan secara paralel untuk mencegah impedansi.

Sumber Daya Bermanfaat

• Elemen yang Mempengaruhi Impedansi Karakteristik PCB dan Solusinya

• Kontrol Impedansi dalam Desain PCB Sirkuit Digital Berkecepatan Tinggi

• Pertimbangan Desain Impedansi untuk PCB Flex-Rigid

• Impedansi Kontrol Vias dan Pengaruhnya pada Integritas Sinyal dalam Desain PCB

• Layanan Pembuatan PCB Fitur Lengkap dari PCBCart - Beberapa opsi Nilai tambah

• Layanan Perakitan PCB Tingkat Lanjut dari PCBCart - Mulai dari 1 buah