Verilog

Verilog adalah jenis Bahasa Deskripsi Perangkat Keras (HDL). Verilog adalah salah satu dari dua bahasa yang digunakan oleh pendidikan dan bisnis untuk merancang FPGA dan ASIC. Jika Anda tidak terbiasa dengan cara kerja FPGA dan ASIC, Anda harus membaca halaman ini untuk pengenalan FPGA dan ASIC. Verilog dan VHDL adalah dua HDL yang paling populer digunakan. Dibandingkan dengan bahasa perangkat lunak tradisional seperti Java atau C, Verilog bekerja sangat berbeda. Mari kita mulai dengan melihat contoh sederhana.

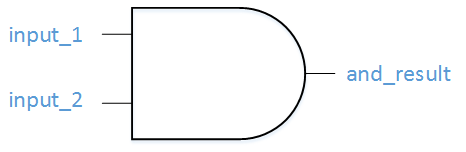

Pertama kita akan membuat file Verilog yang deskripsikan sebuah Dan Gerbang. Sebagai penyegaran, And Gate yang sederhana memiliki dua input dan satu output. Outputnya sama dengan 1 hanya jika kedua inputnya sama dengan 1. Di bawah ini adalah gambar Gerbang And yang akan kita gambarkan dengan Verilog.

An Dan Gerbang

An Dan Gerbang Mari kita lakukan! Satu unit dasar Verilog disebut kawat. Untuk saat ini, mari kita asumsikan bahwa kawat hanya dapat berupa 0 atau 1. Berikut ini beberapa logika kawat dasar:

wire and_temp; assign and_temp = input_1 & input_2;

Kami membuat kawat yang disebut and_temp pada baris kode pertama. Pada baris kedua kode, kami mengambil kabel yang kami buat dan kami menetapkan kawat. Untuk menetapkannya, kami menggunakan fungsi Boolean AND yang di Verilog adalah Ampersand (&). Jika Anda mendeskripsikan kode yang ditampilkan di atas, Anda dapat mengatakan, "Sinyal dan_temp mendapat input_1 DAN diedit dengan input_2."

Input_1 dan Input_2 adalah input ke bagian Kode Verilog ini. Mari kita tunjukkan daftar lengkap input dan output. Ini dilakukan di modul definisi. Modul adalah kata kunci yang dicadangkan di Verilog yang menunjukkan pembuatan blok kode dengan input dan output yang ditentukan.

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

Ini adalah modul dasar Anda. Ini mendefinisikan modul kami yang disebut example_and_gate dan 3 sinyal, 2 input dan 1 output. Mari kita kumpulkan semuanya untuk menyelesaikan file. Satu-satunya hal yang kita lewatkan adalah penugasan output and_result . Satu catatan lain, // di Verilog digunakan untuk komentar.

///////////////////////////////////////////////////////////////////////////////

// File Downloaded from http://www.nandland.com

///////////////////////////////////////////////////////////////////////////////

module example_and_gate

(

input_1,

input_2,

and_result);

input input_1;

input input_2;

output and_result;

wire and_temp;

assign and_temp = input_1 & input_2;

assign and_result = and_temp;

endmodule // example_and_gate

Selamat! Anda telah membuat file Verilog pertama Anda.

Apakah sepertinya Anda harus menulis banyak kode hanya untuk membuat gerbang dan gerbang yang bodoh? Pertama-tama, dan gerbang tidak bodoh. Kedua, Anda benar, HDL membutuhkan banyak kode untuk melakukan tugas yang relatif sederhana. Anda dapat mengambil beberapa kenyamanan dalam kenyataan bahwa Verilog setidaknya kurang verbose dari VHDL. Biasakan diri Anda dengan kenyataan bahwa melakukan sesuatu yang sangat mudah dalam perangkat lunak akan membawa Anda lebih lama secara signifikan dalam HDL seperti Verilog atau VHDL. Tapi minta saja beberapa perangkat lunak untuk mencoba menghasilkan gambar ke monitor VGA yang menampilkan Game of Life Conway dan lihat kepala mereka berputar dengan takjub! Omong-omong, video itu dibuat dengan FPGA. Anda akan dapat melakukannya segera!

Verilog

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang

Desain module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else