Verilog

Sebelum kita melihat lebih detail bahasa Verilog, ada baiknya untuk memahami berbagai lapisan abstraksi dalam desain chip.

Lapisan atas adalah arsitektur tingkat sistem yang mendefinisikan berbagai sub-blok dan mengelompokkannya berdasarkan fungsionalitas. Misalnya, kluster prosesor akan memiliki banyak inti, blok cache, dan logika koherensi cache. Semua ini akan dienkapsulasi dan direpresentasikan sebagai satu blok dengan sinyal input-output.

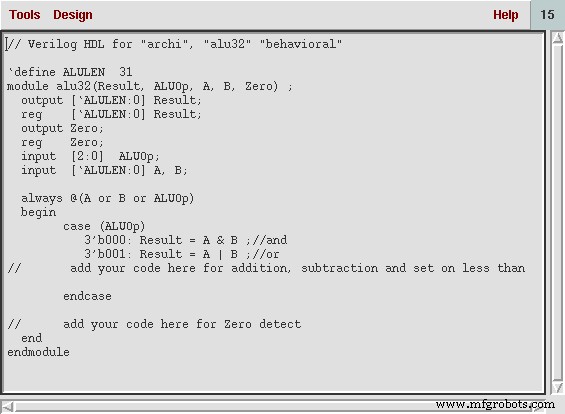

Di tingkat berikutnya, setiap sub-blok ditulis dalam bahasa deskripsi perangkat keras untuk secara akurat menggambarkan fungsionalitas setiap blok individu. Detail implementasi tingkat yang lebih rendah seperti skema sirkuit, perpustakaan teknologi diabaikan pada tahap ini. Misalnya, blok pengontrol akan memiliki beberapa file Verilog yang masing-masing menjelaskan komponen fungsinya yang lebih kecil.

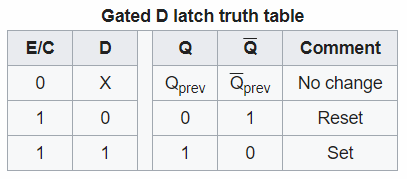

HDL kemudian dikonversi ke skema tingkat gerbang yang juga melibatkan perpustakaan teknologi yang mencirikan elemen digital seperti sandal jepit. Misalnya, rangkaian digital untuk kait D berisi gerbang NAND yang diatur sedemikian rupa sehingga semua kombinasi input D dan E menghasilkan output Q yang diberikan oleh tabel kebenaran.

Tabel kebenaran pada dasarnya memberikan permutasi dari semua level sinyal input dan level output yang dihasilkan dan yang diberikan di bawah ini adalah untuk kait D dengan pin aktif. Skema perangkat keras juga dapat diturunkan dari tabel kebenaran menggunakan logika boolean dan K-maps. Namun, tidak praktis untuk mengikuti metode ini untuk blok digital yang lebih kompleks seperti prosesor dan pengontrol.

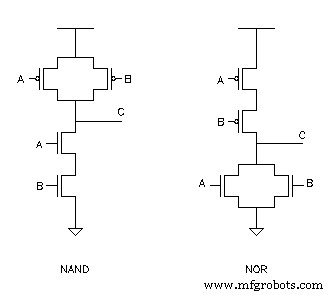

Implementasi gerbang NAND dilakukan dengan menghubungkan transistor CMOS dalam format tertentu. Pada tingkat ini, lebar saluran transistor, Vdd dan kemampuan untuk menggerakkan beban kapasitif keluaran diperhitungkan selama proses desain.

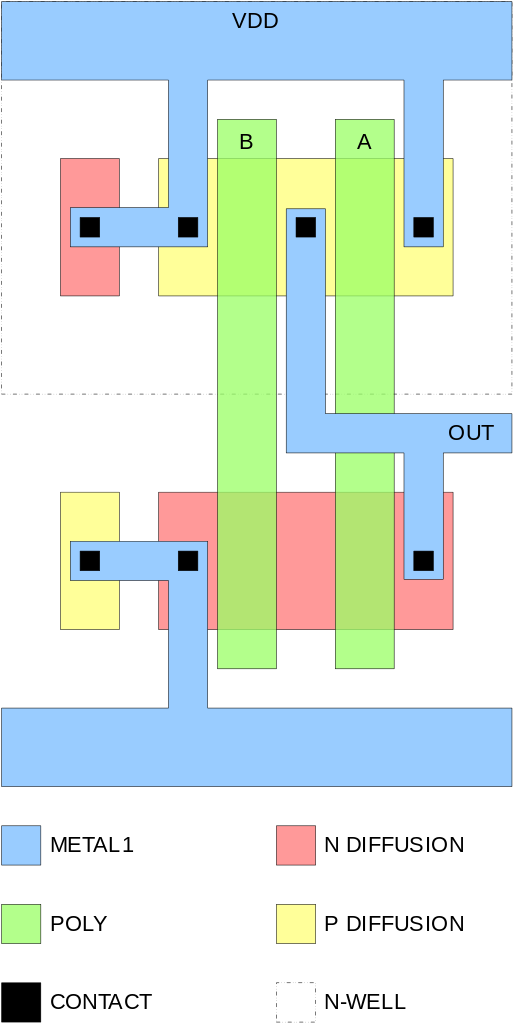

Langkah terakhir adalah tata letak transistor ini dalam silikon menggunakan alat EDA sehingga dapat difabrikasi. Pada tingkat ini, beberapa perangkat dan pengetahuan teknologi akan diperlukan karena tata letak yang berbeda pada akhirnya memiliki sifat fisik yang berbeda seperti resistansi dan kapasitansi di antara implikasi lainnya.

Selanjutnya, ada dua gaya utama yang diikuti dalam desain blok digital, yaitu metodologi top-down dan bottom-up.

Top-DownDalam gaya ini, blok tingkat atas pertama kali didefinisikan bersama dengan identifikasi sub-modul yang diperlukan untuk membangun blok atas. Demikian pula, masing-masing sub-blok dibagi lagi menjadi komponen yang lebih kecil, dan proses berlanjut sampai kita mencapai sel daun atau tahap di mana ia tidak dapat dibagi lagi.

Bottom-upDalam hal ini, tugas pertama adalah mengidentifikasi blok bangunan yang tersedia. Kemudian mereka disatukan dan dihubungkan dengan cara tertentu untuk membangun sel yang lebih besar dan digunakan untuk menyatukan blok tingkat atas.

Biasanya, kombinasi dari kedua aliran digunakan. Arsitek menentukan tampilan tingkat sistem dari desain, dan desainer menerapkan logika masing-masing blok fungsional dan disintesis menjadi gerbang. Gaya top-down diikuti sampai titik ini. Namun, gerbang ini telah dibangun mengikuti aliran bottom-up di mana dimulai dengan tata letak fisik blok terkecil di area, kinerja, dan kekuatan terbaik. Sel standar ini juga memiliki skema perangkat keras dan dapat digunakan untuk memperoleh berbagai informasi seperti waktu naik dan turun, daya, dan penundaan lainnya. Sel-sel ini tersedia untuk alat sintesis yang mengambil dan membuat instance mereka jika diperlukan.

Verilog

Di masa lalu, seorang insinyur akan membuat bagian atau produk dengan mengembangkan gambar di CAD. Gambar tersebut akan merupakan hasil dari pengalaman, imajinasi (kreativitas) insinyur itu, dan data historis (bagaimana bagian-bagian serupa pernah dibuat sebelumnya). Desain generatif adalah optimasi

Desain Roll Pass Produk panjang biasanya digulung dalam beberapa lintasan, yang jumlahnya ditentukan oleh rasio bahan baja input awal (billet persegi atau bulat atau mekar) dan penampang akhir produk jadi. Luas penampang berkurang di setiap lintasan dan bentuk serta ukuran material baja yang dig

Tingkat semangat adalah alat yang sangat tua, digunakan oleh tukang kayu, pembangun, dan bahkan orang-orang di rumah yang mencoba menggantung lukisan, yang membantu Anda menentukan garis lurus atau tegak lurus. Ini juga disebut level gelembung karena tujuan saat Anda berbaris secara horizontal adala

Desain holistik adalah pendekatan desain yang menganggap sistem yang dirancang sebagai satu kesatuan yang saling berhubungan yang juga merupakan bagian dari sesuatu yang lebih besar. Konsep holistik dapat diterapkan pada arsitektur serta desain perangkat mekanis, tata letak ruang, dan sebagainya. Pe