Verilog

Semua kode perilaku ditulis di dalam module dan endmodule . Jadi, desain digital apa pun yang ingin Anda buat, itu akan masuk ke dalam module memblokir. Mungkin atau mungkin tidak memiliki port yang ditentukan - izinkan sinyal masuk ke blok sebagai input atau keluar dari blok sebagai output .

Modul kosong pada contoh di bawah ini disebut testbench . Anda dapat memberi nama apa pun yang Anda suka, kecuali bahwa itu harus berupa alfanumerik, dan dapat berisi '_'.

module testbench;

endmodule

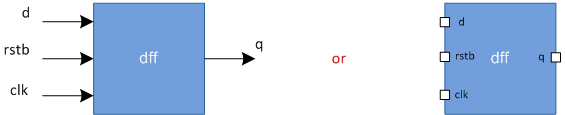

Mari kita lihat modul lain. Ini memiliki beberapa sinyal (d, clk, rstb ) dideklarasikan sebagai input dan q dideklarasikan sebagai output.

module dff (input d,

clk,

rstb,

output q);

endmodule

Sekarang kita telah melihat bagaimana sebuah modul terlihat, mari kita lihat apa yang dapat dimasukkan ke dalam sebuah modul, dengan melihat modul testbench sekali lagi. Ada dua jenis tipe data di Verilog:

reg tipe data digunakan untuk menyimpan nilai seperti variabel, sedangkan wire hanya analog dengan kabel listrik, yang harus didorong terus menerus. Jadi biasanya wire digunakan untuk menghubungkan antara beberapa modul, dan sinyal lainnya.

module testbench;

reg d;

reg rst_b;

reg clk;

wire q;

endmodule

Verilog memiliki tiga blok dasar :

always @ (kondisi ) | selalu dijalankan jika kondisi terpenuhi |

initial | hanya akan dieksekusi sekali, saat simulasi dimulai |

assign [Kiri] =[Kanan] | Nilai LHS akan diperbarui setiap kali RHS berubah |

Ada beberapa aturan yang perlu diingat saat menulis Verilog:

reg dapat ditetapkan hanya dalam initial dan always blokwire dapat diberi nilai hanya melalui assign pernyataanbegin .. end

module testbench;

reg d;

reg rst_b;

reg clk;

wire q;

initial begin

d = 0;

rst_b = 0;

clk = 0;

#100 $finish;

end

always begin

#10 clk = ~clk;

end

endmodule

Catatan berikut dari contoh yang ditunjukkan di atas:

initial blokir, mulai dan akhir digunakanreg always blok, itu akan berjalan seperti loop tak terbatas di Cclk = ~clk; akan mengaktifkan nilai jam, dan karena #10 diletakkan sebelum pernyataan, jam akan berubah setelah setiap 10 satuan waktu.$finish adalah cara untuk mengakhiri simulasi. Dalam hal ini, itu akan berjalan selama 100 unit waktu dan keluar.Verilog

Sebuah for loop adalah loop yang paling banyak digunakan dalam perangkat lunak, tetapi terutama digunakan untuk mereplikasi logika perangkat keras di Verilog. Ide di balik for loop adalah untuk mengulangi satu set pernyataan yang diberikan dalam loop selama kondisi yang diberikan benar. Ini sangat m

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang