Verilog

Satu set pernyataan Verilog biasanya dieksekusi secara berurutan dalam simulasi. Pernyataan ini ditempatkan di dalam prosedur memblokir. Terutama ada dua jenis prosedur blok di Verilog - awal dan selalu

initial

[single statement]

initial begin

[multiple statements]

end

Sebuah initial blok tidak dapat disintesis dan karenanya tidak dapat diubah menjadi skema perangkat keras dengan elemen digital. Oleh karena itu blok awal tidak melayani banyak tujuan selain untuk digunakan dalam simulasi. Blok ini terutama digunakan untuk menginisialisasi variabel dan mendorong port desain dengan nilai tertentu.

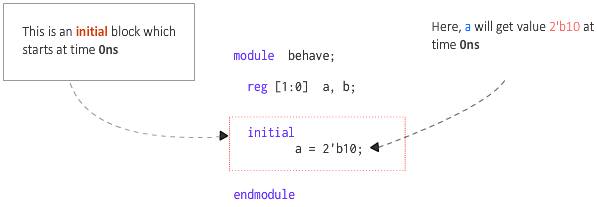

Sebuah initial blok dimulai pada awal simulasi pada waktu 0 unit. Blok ini akan dieksekusi hanya sekali selama seluruh simulasi. Eksekusi initial blok selesai setelah semua pernyataan dalam blok dieksekusi.

Gambar di atas memiliki module disebut berperilaku yang memiliki dua sinyal internal yang disebut a dan b. initial blok hanya memiliki satu pernyataan dan karenanya tidak perlu menempatkan pernyataan di dalam begin dan end . Pernyataan ini memberikan nilai 2'b10 ke a ketika blok awal dimulai pada waktu 0 unit.

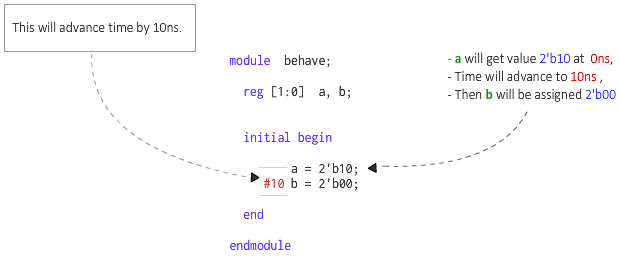

Kode yang ditunjukkan di bawah ini memiliki pernyataan tambahan yang memberikan beberapa nilai pada sinyal b. Namun ini terjadi hanya setelah 10 unit waktu dari eksekusi pernyataan sebelumnya. Ini berarti bahwa a ditetapkan terlebih dahulu dengan nilai yang diberikan dan kemudian setelah 10 unit waktu, b ditetapkan ke 0.

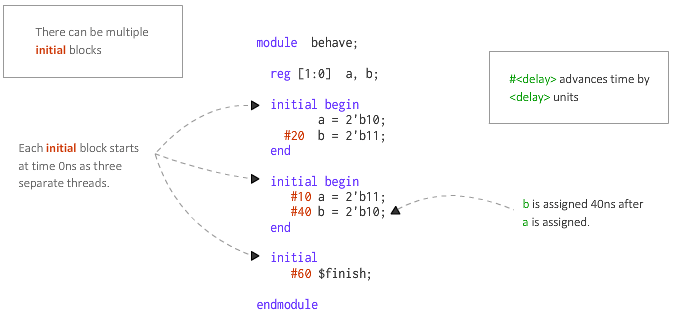

Tidak ada batasan jumlah initial blok yang dapat didefinisikan di dalam modul.

Kode yang ditunjukkan di bawah ini memiliki tiga initial blok yang semuanya dimulai pada saat yang sama dan dijalankan secara paralel. Namun, tergantung pada pernyataan dan penundaan dalam setiap blok awal, waktu yang dibutuhkan untuk menyelesaikan blok dapat bervariasi.

Pada contoh ini, blok pertama memiliki delay 20 unit, sedangkan blok kedua memiliki total delay 50 unit (10 + 40) dan blok terakhir memiliki delay 60 unit. Oleh karena itu simulasi membutuhkan 60 unit waktu untuk diselesaikan karena setidaknya ada satu blok awal yang masih berjalan hingga 60 unit waktu.

$finish adalah tugas sistem Verilog yang memberitahu simulator untuk menghentikan simulasi saat ini.

Jika blok terakhir memiliki penundaan 30 unit waktu seperti yang ditunjukkan di bawah ini, simulasi akan berakhir pada 30 unit waktu sehingga membunuh semua initial lainnya blok yang aktif pada saat itu.

initial begin

#30 $finish;

end

Lihat contoh flash yang ditunjukkan di bawah ini untuk melihat bagaimana initial blok dieksekusi dalam simulasi.

Klik di sini untuk slideshow dengan contoh simulasi !

Verilog

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang

Desain module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else