Verilog Blok pernyataan

Ada beberapa cara untuk mengelompokkan sekumpulan pernyataan bersama-sama yang secara sintaksis setara dengan satu pernyataan dan dikenal sebagai pernyataan blok . Ada dua jenis pernyataan blok:berurutan dan paralel.

Sequential

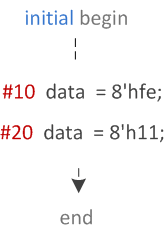

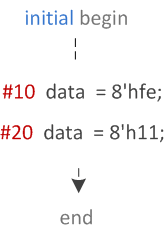

Pernyataan dibungkus menggunakan begin dan end kata kunci dan akan dieksekusi secara berurutan dalam urutan yang diberikan, satu demi satu. Nilai penundaan diperlakukan relatif terhadap waktu eksekusi pernyataan sebelumnya. Setelah semua pernyataan di dalam blok dieksekusi, kontrol dapat diteruskan ke tempat lain.

module design0;

bit [31:0] data;

// "initial" block starts at time 0

initial begin

// After 10 time units, data becomes 0xfe

#10 data = 8'hfe;

$display ("[Time=%0t] data=0x%0h", $time, data);

// After 20 time units, data becomes 0x11

#20 data = 8'h11;

$display ("[Time=%0t] data=0x%0h", $time, data);

end

endmodule

Pada contoh di atas, pernyataan pertama di begin-end blok akan dieksekusi pada 10 satuan waktu, dan pernyataan kedua pada 30 satuan waktu karena sifat relatif. Ini adalah 20 unit waktu setelah eksekusi pernyataan sebelumnya.

Log Simulasi

ncsim> run

[Time=10] data=0xfe

[Time=30] data=0x11

ncsim: *W,RNQUIE: Simulation is complete.

Sejajar

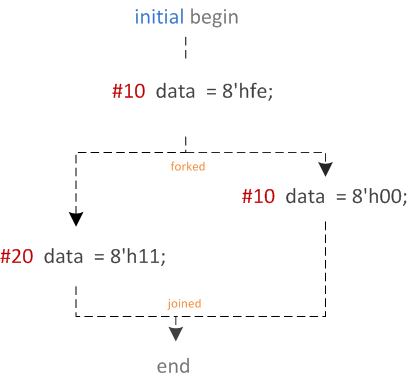

Sebuah sejajar blok dapat mengeksekusi pernyataan secara bersamaan dan kontrol penundaan dapat digunakan untuk menyediakan urutan waktu tugas. Pernyataan diluncurkan secara paralel dengan membungkusnya dalam fork dan join kata kunci.

initial begin

#10 data = 8'hfe;

fork

#20 data = 8'h11;

#10 data = 8'h00;

join

end

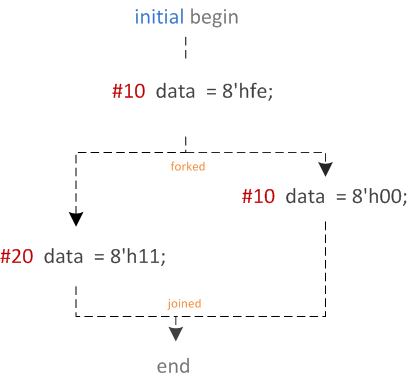

Pada contoh di atas, fork-join blok akan diluncurkan setelah mengeksekusi pernyataan pada 10 unit waktu. Pernyataan dalam blok ini akan dieksekusi secara paralel dan pernyataan pertama yang akan diluncurkan adalah pernyataan di mana data diberi nilai 8'h00 karena penundaan untuk itu adalah 10 unit waktu setelah peluncuran fork-join. Setelah 10 unit waktu lagi, pernyataan pertama akan diluncurkan dan data akan mendapatkan nilai 8'h11.

initial begin

#10 data = 8'hfe;

fork

#10 data = 8'h11;

begin

#20 data = 8'h00;

#30 data = 8'haa;

end

join

end

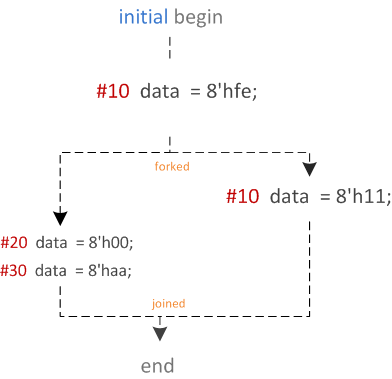

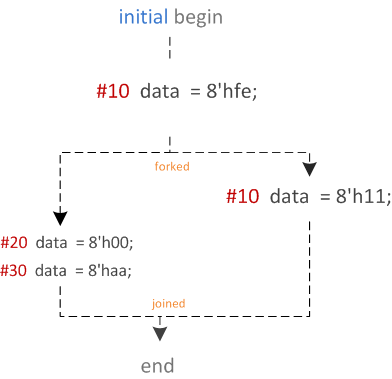

Ada begin-end blok pada contoh di atas, dan semua pernyataan dalam blok awal-akhir akan dieksekusi secara berurutan, tetapi blok itu sendiri akan diluncurkan secara paralel bersama dengan pernyataan lainnya. Jadi, data akan mendapatkan 8'h11 pada 20 satuan waktu, 8'h00 pada 30 satuan waktu dan 8'haa pada 60 satuan waktu.

Penamaan blok

Baik blok sekuensial maupun paralel dapat diberi nama dengan menambahkan : name_of_block setelah kata kunci begin dan fork . Dengan demikian, blok dapat direferensikan dalam disable pernyataan.

begin : name_seq

[statements]

end

fork : name_fork

[statements]

join