Verilog

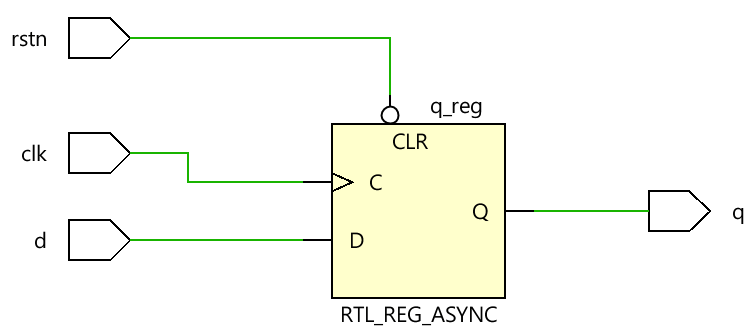

A D flip-flop adalah elemen berurutan yang mengikuti pin input d di tepi jam tertentu.

module dff ( input d,

input rstn,

input clk,

output reg q);

always @ (posedge clk or negedge rstn)

if (!rstn)

q <= 0;

else

q <= d;

endmodule

module tb_dff;

reg clk;

reg d;

reg rstn;

reg [2:0] delay;

dff dff0 ( .d(d),

.rsnt (rstn),

.clk (clk),

.q (q));

// Generate clock

always #10 clk = ~clk;

// Testcase

initial begin

clk <= 0;

d <= 0;

rstn <= 0;

#15 d <= 1;

#10 rstn <= 1;

for (int i = 0; i < 5; i=i+1) begin

delay = $random;

#(delay) d <= i;

end

end

endmodule

module dff ( input d,

input rstn,

input clk,

output reg q);

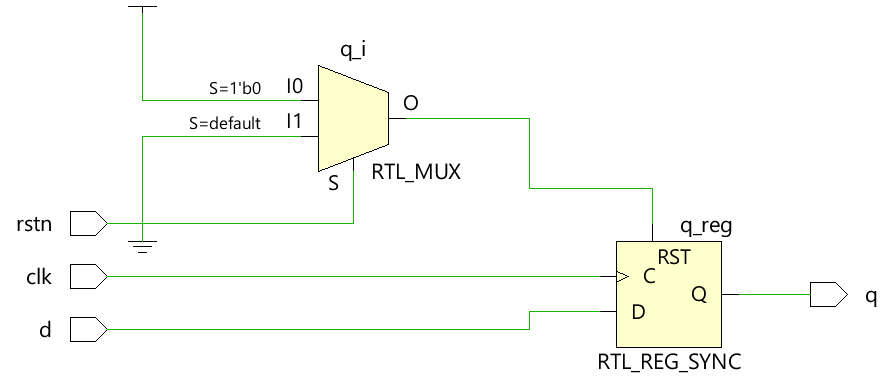

always @ (posedge clk)

if (!rstn)

q <= 0;

else

q <= d;

endmodule

module tb_dff;

reg clk;

reg d;

reg rstn;

reg [2:0] delay;

dff dff0 ( .d(d),

.rsnt (rstn),

.clk (clk),

.q (q));

// Generate clock

always #10 clk = ~clk;

// Testcase

initial begin

clk <= 0;

d <= 0;

rstn <= 0;

#15 d <= 1;

#10 rstn <= 1;

for (int i = 0; i < 5; i=i+1) begin

delay = $random;

#(delay) d <= i;

end

end

endmodule

Verilog

Desain module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+1) b

Desain module johnson_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= ~out[0]; for (int i = 0; i < WIDTH-1; i=i+1

RESET setelah Edit Program di Fanuc TC Teknisi CNC harus selalu ingat untuk menekan tombol RESET sebelum menekan CYCLE START pada mesin cnc dengan kontrol cnc FANUC TC (mis. Gildemeister NEF 560), jika mereka membuat perubahan pada program bagian cnc mereka.

Kode M Heidenhain ( Fungsi lain-lain) untuk Heidenhain TNC 640/530/410/426/430/320 Heidenhain TNC 320 Kode Heidenhain M Kode M Deskripsi M0 Hentikan program berjalan (Spindle STOP, Coolant OFF) M1 Program opsional STOP (Spindle STOP, Coolant OFF) M2 Hentikan program berjalan (Spindle STOP,Coola