Verilog

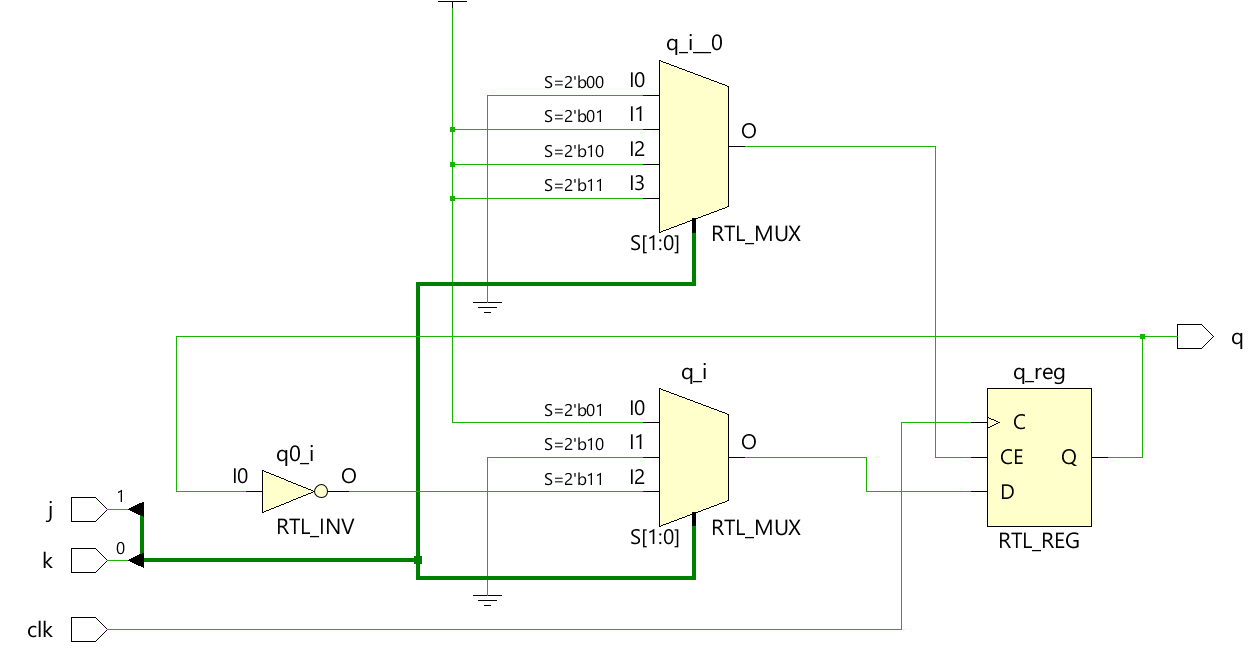

module jk_ff ( input j,

input k,

input clk,

output q);

reg q;

always @ (posedge clk)

case ({j,k})

2'b00 : q <= q;

2'b01 : q <= 0;

2'b10 : q <= 1;

2'b11 : q <= ~q;

endcase

endmodule

module tb_jk;

reg j;

reg k;

reg clk;

always #5 clk = ~clk;

jk_ff jk0 ( .j(j),

.k(k),

.clk(clk),

.q(q));

initial begin

j <= 0;

k <= 0;

#5 j <= 0;

k <= 1;

#20 j <= 1;

k <= 0;

#20 j <= 1;

k <= 1;

#20 $finish;

end

initial

$monitor ("j=%0d k=%0d q=%0d", j, k, q);

endmodule

Verilog

Desain module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+1) b

Desain module johnson_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= ~out[0]; for (int i = 0; i < WIDTH-1; i=i+1

Komponen dan persediaan Arduino Nano R3 × 1 Maxim Integrated DS3231M - ±5ppm, I2C Real-Time Clock × 1 Matriks LED 8x8 dengan driver MAX7219 × 1 Katoda Umum Difusi RGB × 1 Resistor 220 ohm × 2 Rotary Encoder dengan Tombol Tekan × 1

Apakah Anda tertarik untuk mempelajari atau membuat rangkaian digital seperti yang terdapat pada komputer, peralatan komunikasi, dan sistem sejenis lainnya? Hal pertama yang harus dilihat adalah transistor flip flop. Blok bangunan fundamental dari flip flop adalah gerbang logika, yang merupakan mod