Singkatnya, VHDL adalah bahasa komputer yang digunakan untuk merancang sirkuit digital. Saya menggunakan istilah bahasa komputer untuk membedakan VHDL dari bahasa pemrograman lain yang lebih umum seperti Java atau C++. Tetapi apakah VHDL adalah bahasa pemrograman? Ya itu. Ini adalah bahasa pemro

Meskipun alat VHDL dan FPGA seringkali sangat mahal, mudah untuk mengakses perangkat lunak canggih secara gratis jika Anda seorang pelajar. Ada beberapa simulator, editor, dan IDE untuk bekerja dengan VHDL. Artikel ini menunjukkan cara menginstal dua program paling populer yang digunakan oleh insiny

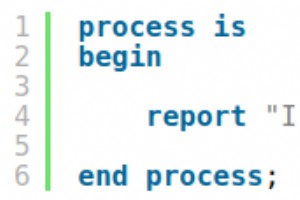

Saat mempelajari bahasa pemrograman baru, saya selalu suka memulai dengan belajar cara mencetak. Saat Anda menguasai keluaran Hello World!, Anda tahu bahwa Anda telah membuat lingkungan bekerja. Ini juga menunjukkan kerangka dasar bahasa, kode minimum yang diperlukan untuk menghasilkan keluaran apa

Pada tutorial sebelumnya kita telah mempelajari bahwa sebuah proses dapat dianggap sebagai sebuah program thread. Kami juga mengetahui bahwa wait; pernyataan menyebabkan program berhenti tanpa batas. Tetapi apakah ada cara untuk membuat program menunggu nilai waktu selain selamanya? Jika kita mengh

Pada tutorial sebelumnya kita telah mempelajari cara menunda waktu menggunakan wait for penyataan. Kami juga belajar tentang loop proses. Sekarang kita tahu bahwa jika kita membiarkannya, proses utas akan berulang dalam proses selamanya. Tetapi bagaimana jika kita ingin melakukan sesuatu sekali saj

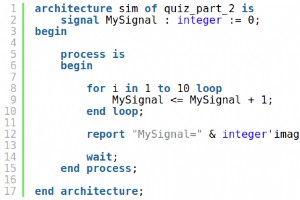

Pada tutorial sebelumnya kita belajar membuat infinite loop dengan menggunakan loop penyataan. Kami juga mempelajari cara keluar dari loop dengan menggunakan exit penyataan. Tetapi bagaimana jika kita ingin loop berulang beberapa kali? For-Loop adalah cara termudah untuk melakukannya. For-Loop memu

Dalam tutorial sebelumnya, kita belajar bagaimana menggunakan For-Loop untuk melakukan iterasi pada rentang integer. Tetapi bagaimana jika kita menginginkan kontrol loop yang lebih rinci daripada sekadar rentang bilangan bulat tetap? Kita bisa menggunakan While-Loop untuk ini. While-Loop akan terus

Jadi, Anda telah menyelesaikan bagian pertama dari seri Tutorial VHDL Dasar. Selamat! Anda hanya berjam-jam lagi untuk menjadi jagoan VHDL asli. Tetapi Anda telah menyelesaikan langkah pertama, dan itulah bagian terpenting sekarang! Sebelum kita melangkah lebih jauh, Anda harus menguji kemampuan An

Pada tutorial sebelumnya kita telah belajar bagaimana mendeklarasikan sebuah variabel dalam sebuah proses. Variabel bagus untuk membuat algoritme dalam suatu proses, tetapi tidak dapat diakses oleh dunia luar. Jika ruang lingkup variabel hanya dalam satu proses, bagaimana ia dapat berinteraksi denga

Dalam tutorial sebelumnya kita mempelajari perbedaan utama antara sinyal dan variabel. Kami belajar bahwa sinyal memiliki cakupan yang lebih luas daripada variabel, yang hanya dapat diakses dalam satu proses. Jadi bagaimana kita bisa menggunakan sinyal untuk komunikasi antara beberapa proses? Kami

Dalam tutorial sebelumnya kami menggunakan ekspresi kondisional dengan pernyataan Tunggu Sampai. Ekspresi memastikan bahwa proses hanya dipicu ketika dua sinyal penghitung sama. Tetapi bagaimana jika kita ingin program dalam suatu proses mengambil tindakan yang berbeda berdasarkan masukan yang berbe

Anda harus selalu menggunakan daftar sensitivitas untuk memicu proses dalam modul produksi. Daftar sensitivitas adalah parameter untuk proses yang mencantumkan semua sinyal yang sensitif terhadap proses tersebut. Jika ada sinyal yang berubah, proses akan aktif, dan kode di dalamnya akan dieksekusi.

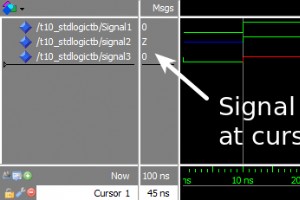

Jenis yang paling umum digunakan dalam VHDL adalah std_logic . Pikirkan jenis ini sebagai bit tunggal, informasi digital yang dibawa oleh kabel fisik tunggal. std_logic memberi kami kontrol yang lebih halus atas sumber daya dalam desain kami daripada integer jenis, yang telah kita gunakan di tutoria

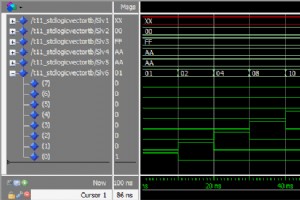

std_logic_vector type dapat digunakan untuk membuat bus sinyal di VHDL. std_logic adalah jenis yang paling umum digunakan dalam VHDL, dan std_logic_vector adalah versi lariknya. Sedangkan std_logic sangat bagus untuk memodelkan nilai yang dapat dibawa oleh satu kabel, sangat tidak praktis untuk men

Uji keterampilan coding Anda dengan kuis VHDL ini setelah menyelesaikan tutorial 6-11 dari seri Tutorial VHDL Dasar! Jika Anda membaca posting blog, menonton video, dan melakukan latihan, Anda harus memenuhi syarat untuk menjawab sebagian besar pertanyaan dalam kuis. Kuis ini sengaja dibuat sedikit

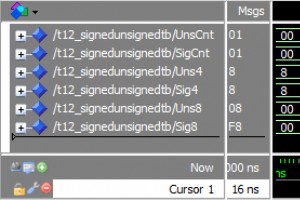

Tipe yang ditandatangani dan tidak ditandatangani dalam VHDL adalah vektor bit, sama seperti tipe std_logic_vector. Perbedaannya adalah meskipun std_logic_vector sangat bagus untuk mengimplementasikan bus data, std_logic_vector tidak berguna untuk melakukan operasi aritmatika. Jika Anda mencoba men

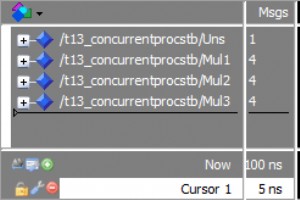

Pernyataan bersamaan dalam VHDL adalah penugasan sinyal dalam arsitektur, tetapi di luar konstruksi proses normal. Pernyataan konkuren juga disebut sebagai penugasan konkuren atau proses konkuren. Saat Anda membuat pernyataan bersamaan, Anda sebenarnya sedang membuat proses dengan karakteristik ter

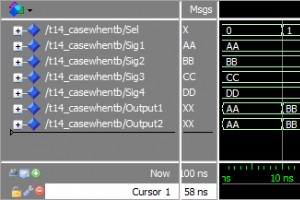

Pernyataan Case-When akan menyebabkan program mengambil satu dari beberapa jalur yang berbeda, tergantung pada nilai sinyal, variabel, atau ekspresi. Ini adalah alternatif yang lebih elegan untuk pernyataan If-then-Elsif-Else dengan beberapa Elsif. Bahasa pemrograman lain memiliki konstruksi serupa

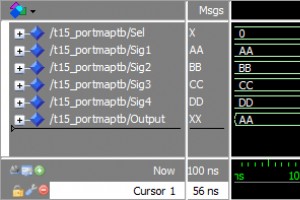

Modul adalah unit mandiri dari kode VHDL. Modul berkomunikasi dengan dunia luar melalui entitas . Peta pelabuhan adalah bagian dari instantiasi modul tempat Anda mendeklarasikan sinyal lokal mana yang akan dihubungkan dengan input dan output modul. Dalam tutorial sebelumnya dalam seri ini kami tela

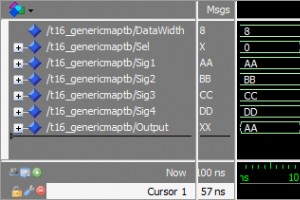

Membuat modul adalah cara yang bagus untuk menggunakan kembali kode, tetapi seringkali Anda memerlukan modul yang sama dengan variasi yang lebih kecil di seluruh desain Anda. Inilah gunanya generik dan peta generik. Ini memungkinkan Anda untuk membuat bagian-bagian tertentu dari modul dapat dikonfig

VHDL