VHDL memiliki generator pseudo-acak built-in, tetapi hanya dapat menghasilkan angka floating-point antara 0 dan 1. Untungnya, Anda dapat memperoleh dari jenis format data acak lain yang Anda perlukan. Lanjutkan membaca artikel ini untuk mengetahui cara menghasilkan real atau integer nilai rentang ap

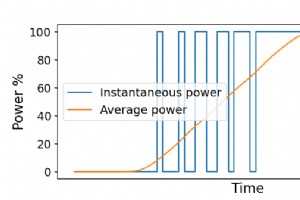

Modulasi lebar pulsa (PWM) adalah cara yang efisien untuk mengontrol elektronik analog dari pin FPGA digital murni. Alih-alih mencoba mengatur tegangan analog, PWM dengan cepat menghidupkan dan mematikan arus suplai dengan daya penuh ke perangkat analog. Metode ini memberi kita kontrol yang tepat at

Saya perhatikan bahwa banyak gadget yang saya beli beberapa tahun terakhir telah beralih dari kedipan LED ke pernapasan led. Sebagian besar alat elektronik berisi LED status yang perilakunya memberikan indikasi tentang apa yang terjadi di dalam perangkat. Sikat gigi elektrik saya berkedip LED ketik

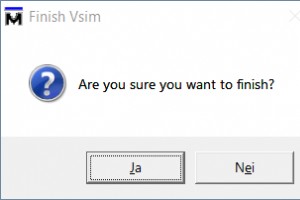

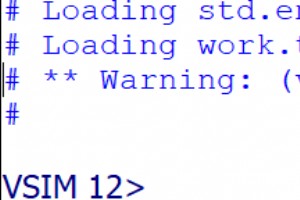

Bagaimana Anda menghentikan simulator VHDL ketika simulasi selesai? Ada beberapa cara untuk melakukannya. Dalam artikel ini, kita akan membahas cara paling umum untuk mengakhiri uji coba yang sukses. Kode VHDL yang disajikan di sini bersifat universal, dan harus berfungsi di semua simulator VHDL ya

Kebanyakan simulator VHDL menggunakan Tool Command Language (Tcl) sebagai bahasa scripting mereka. Saat Anda mengetik perintah di konsol simulator, Anda menggunakan Tcl. Selanjutnya, Anda dapat membuat skrip dengan Tcl yang berjalan di simulator dan berinteraksi dengan kode VHDL Anda. Dalam artikel

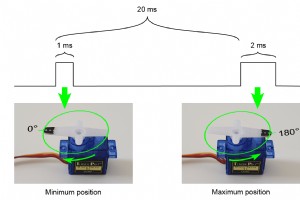

Servo model yang dikendalikan radio (RC) adalah aktuator kecil yang biasanya digunakan dalam model pesawat, mobil, dan kapal penghobi. Mereka memungkinkan operator untuk mengontrol kendaraan melalui link radio dari jarak jauh. Karena model RC telah ada sejak lama, antarmuka standar de-facto adalah m

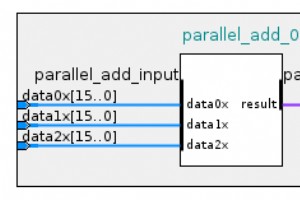

Pernyataan generate dalam VHDL dapat secara otomatis menduplikasi blok kode ke penutupan dengan sinyal, proses, dan instance yang identik. Ini adalah loop for untuk region arsitektur yang dapat membuat proses berantai atau instance modul. Tidak seperti loop for biasa, yang hanya dapat ada dalam p

String teks dalam VHDL umumnya terbatas pada array karakter dengan panjang tetap. Itu masuk akal karena VHDL menjelaskan perangkat keras, dan string dengan panjang generik memerlukan memori dinamis. Untuk mendefinisikan array string, Anda harus mengalokasikan ruang pada waktu kompilasi untuk jumlah

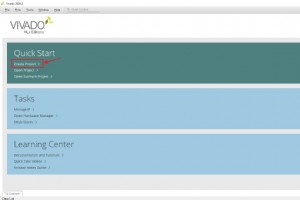

Tutorial ini mencakup penggunaan Integrated Logic Analyzer (ILA) dan Input/Keluaran Virtual (VIO) core untuk men-debug dan memantau desain VHDL Anda di Xilinx Vivado IDE. Dalam banyak kasus, desainer perlu melakukan verifikasi on-chip. Artinya, mendapatkan akses ke perilaku sinyal internal dalam de

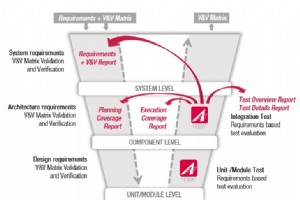

Saat mendesain VHDL untuk aplikasi FPGA yang kritis terhadap keamanan, menulis testbenches dengan upaya terbaik saja tidak cukup. Anda harus menunjukkan bukti bahwa modul berfungsi sebagaimana mestinya dan tanpa efek samping yang tidak diinginkan. Teknik verifikasi formal dapat membantu Anda memeta

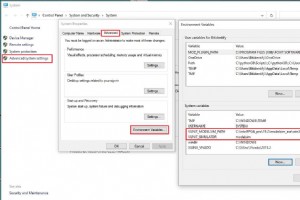

VUnit adalah salah satu kerangka kerja verifikasi VHDL open-source paling populer yang tersedia saat ini. Ini menggabungkan runner suite pengujian Python dengan pustaka VHDL khusus untuk mengotomatiskan bangku pengujian Anda. Untuk memberi Anda tutorial VUnit gratis ini, VHDLwhiz meminta Ahmadmun

Pernahkah Anda ingin menjalankan simulasi VHDL yang menyertakan inti IP Quartus melalui kerangka kerja verifikasi VUnit? Itulah yang ada dalam pikiran insinyur FPGA Konstantinos Paraskevopoulos, tetapi dia tidak dapat menemukan tutorial yang cocok untuk itu. Untungnya, dia menggunakan bakatnya untu

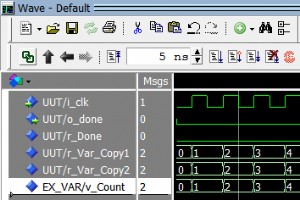

Variabel dalam VHDL bertindak mirip dengan variabel dalam C. Nilainya valid di lokasi yang tepat dalam kode di mana variabel dimodifikasi. Oleh karena itu, jika sinyal menggunakan nilai variabel sebelum tugas, itu akan memiliki nilai variabel lama. Jika sinyal menggunakan nilai variabel setelah tuga

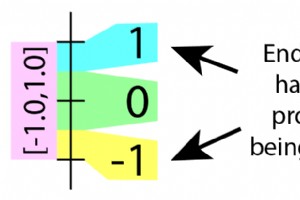

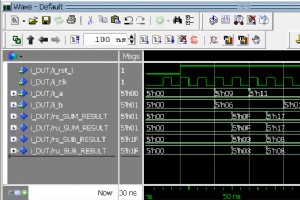

Semua Desainer Digital harus memahami cara kerja matematika di dalam FPGA atau ASIC. Langkah pertama untuk itu adalah memahami cara kerja jenis sinyal yang ditandatangani dan tidak ditandatangani. Jenis yang ditandatangani dan tidak ditandatangani ada di numeric_std paket, yang merupakan bagian dari

Konstruksi Record dalam VHDL dapat digunakan untuk menyederhanakan kode Anda. Catatan mirip dengan struktur di C . Rekaman paling sering digunakan untuk mendefinisikan tipe VHDL baru. Tipe baru ini berisi kelompok sinyal apa pun yang diinginkan pengguna. Paling sering ini digunakan untuk menyederhan

Prosedur adalah bagian dari sekelompok struktur yang disebut subprogram. Prosedur adalah bagian kecil dari kode yang melakukan operasi yang digunakan kembali di seluruh kode Anda. Ini berfungsi untuk membersihkan kode serta memungkinkan penggunaan kembali. Prosedur dapat mengambil input dan menghas

Menggunakan File Paket Numeric_Std dan Std_Logic_Arith Di bawah ini adalah konversi yang paling umum digunakan dalam VHDL. Halaman dipecah menjadi dua bagian. Paruh pertama halaman menunjukkan konversi menggunakan file paket Numeric_Std. Paruh kedua halaman menunjukkan konversi menggunakan file pak

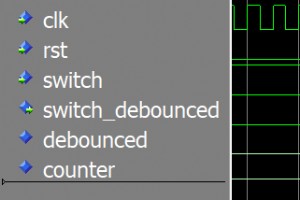

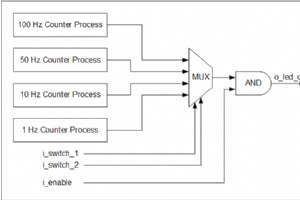

Bagian 1:Desain VHDL atau Verilog Tutorial ini menunjukkan konstruksi kode VHDL dan Verilog yang mengedipkan LED pada frekuensi tertentu. VHDL dan Verilog keduanya ditampilkan, dan Anda dapat memilih mana yang ingin Anda pelajari terlebih dahulu. Setiap kali kode desain ditulis, perancang FPGA perl

Menggunakan Proses VHDL atau Verilog Selalu Memblokir Tutorial ini menunjukkan cara menulis blok VHDL atau Verilog yang terdapat dalam Proses atau Selalu Blokir masing-masing. Proses (dalam VHDL) dan Always Blocks (dalam Verilog) adalah hal mendasar dan perlu dipahami dengan baik. Mereka berperilak

VHDL adalah akronim yang mengerikan. Itu singkatan dari V HSIC H perangkat keras D deskripsi L bahasa. Akronim di dalam akronim, luar biasa! VHSIC adalah singkatan dari V ery H tinggi S pipis Saya C . terintegrasi irit. Oleh karena itu, VHDL yang diperluas adalah V Sirkuit Terpadu Kecepatan Tinggi H

VHDL

Pengujian perangkat lunak model Imperas untuk Arm sekarang di TESSY Razorcat

Akurasi, Presisi, Toleransi, dan Pertimbangan Pemesinan Logam CNC

Panduan 7 Langkah untuk Memilih Produsen Perakitan PCB yang Tepat - Bagian 2

Mengotomatiskan hutang dagang:RPA, logika fuzzy, dan mengubah daftar hitam menjadi hitam