Saya sedikit terganggu dengan keanehan antarmuka AXI saat pertama kali harus membuat logika untuk antarmuka modul AXI. Alih-alih sinyal kontrol sibuk/valid, penuh/valid, atau kosong/valid biasa, antarmuka AXI menggunakan dua sinyal kontrol bernama siap dan valid. Rasa frustrasi saya segera berubah m

Cara mudah untuk mengisi blok RAM dengan nilai awal adalah dengan membaca literal biner atau heksadesimal dari file ASCII. Ini juga merupakan cara yang baik untuk membuat ROM (memori hanya-baca) di VHDL. Bagaimanapun, RAM dan ROM adalah hal yang sama di FPGA, ROM adalah RAM yang hanya Anda baca. Co

Membaca nilai sinyal dari file adalah cara alternatif untuk menghasilkan rangsangan untuk perangkat yang diuji (DUT). Urutan dan waktu testbench dikodekan dalam file stimulus yang dibaca oleh testbench VHDL, baris demi baris. Ini memungkinkan Anda dengan mudah mengubah pola bentuk gelombang yang ing

Mengonversi file gambar ke format bitmap membuat cara termudah untuk membaca gambar menggunakan VHDL. Dukungan untuk format file gambar grafik raster BMP dibangun ke dalam sistem operasi Microsoft Windows. Itu membuat BMP menjadi format gambar yang cocok untuk menyimpan foto untuk digunakan di bangk

Video ini adalah presentasi pengantar tentang FPGA dan teknologi logika yang dapat diprogram. Saya menyampaikan ceramah selama 45 menit ini di sebuah acara yang diselenggarakan oleh 7 Peaks Software di Bangkok, Thailand, pada 19 November 2019. Sorotan dari presentasi meliputi: 05:07 Siapa yang me

VHDL memiliki generator pseudo-acak built-in, tetapi hanya dapat menghasilkan angka floating-point antara 0 dan 1. Untungnya, Anda dapat memperoleh dari jenis format data acak lain yang Anda perlukan. Lanjutkan membaca artikel ini untuk mengetahui cara menghasilkan real atau integer nilai rentang ap

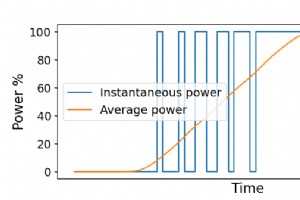

Modulasi lebar pulsa (PWM) adalah cara yang efisien untuk mengontrol elektronik analog dari pin FPGA digital murni. Alih-alih mencoba mengatur tegangan analog, PWM dengan cepat menghidupkan dan mematikan arus suplai dengan daya penuh ke perangkat analog. Metode ini memberi kita kontrol yang tepat at

Saya perhatikan bahwa banyak gadget yang saya beli beberapa tahun terakhir telah beralih dari kedipan LED ke pernapasan led. Sebagian besar alat elektronik berisi LED status yang perilakunya memberikan indikasi tentang apa yang terjadi di dalam perangkat. Sikat gigi elektrik saya berkedip LED ketik

Bagaimana Anda menghentikan simulator VHDL ketika simulasi selesai? Ada beberapa cara untuk melakukannya. Dalam artikel ini, kita akan membahas cara paling umum untuk mengakhiri uji coba yang sukses. Kode VHDL yang disajikan di sini bersifat universal, dan harus berfungsi di semua simulator VHDL ya

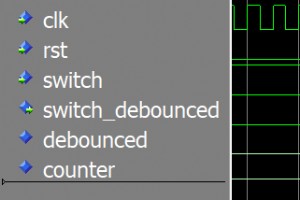

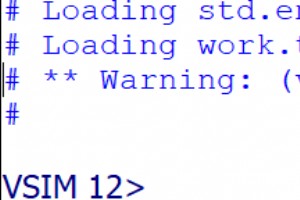

Kebanyakan simulator VHDL menggunakan Tool Command Language (Tcl) sebagai bahasa scripting mereka. Saat Anda mengetik perintah di konsol simulator, Anda menggunakan Tcl. Selanjutnya, Anda dapat membuat skrip dengan Tcl yang berjalan di simulator dan berinteraksi dengan kode VHDL Anda. Dalam artikel

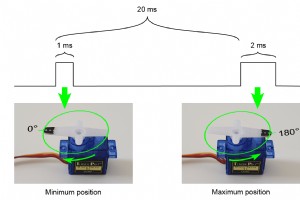

Servo model yang dikendalikan radio (RC) adalah aktuator kecil yang biasanya digunakan dalam model pesawat, mobil, dan kapal penghobi. Mereka memungkinkan operator untuk mengontrol kendaraan melalui link radio dari jarak jauh. Karena model RC telah ada sejak lama, antarmuka standar de-facto adalah m

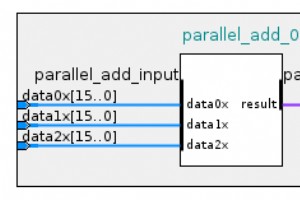

Pernyataan generate dalam VHDL dapat secara otomatis menduplikasi blok kode ke penutupan dengan sinyal, proses, dan instance yang identik. Ini adalah loop for untuk region arsitektur yang dapat membuat proses berantai atau instance modul. Tidak seperti loop for biasa, yang hanya dapat ada dalam p

String teks dalam VHDL umumnya terbatas pada array karakter dengan panjang tetap. Itu masuk akal karena VHDL menjelaskan perangkat keras, dan string dengan panjang generik memerlukan memori dinamis. Untuk mendefinisikan array string, Anda harus mengalokasikan ruang pada waktu kompilasi untuk jumlah

Tutorial ini mencakup penggunaan Integrated Logic Analyzer (ILA) dan Input/Keluaran Virtual (VIO) core untuk men-debug dan memantau desain VHDL Anda di Xilinx Vivado IDE. Dalam banyak kasus, desainer perlu melakukan verifikasi on-chip. Artinya, mendapatkan akses ke perilaku sinyal internal dalam de

Saat mendesain VHDL untuk aplikasi FPGA yang kritis terhadap keamanan, menulis testbenches dengan upaya terbaik saja tidak cukup. Anda harus menunjukkan bukti bahwa modul berfungsi sebagaimana mestinya dan tanpa efek samping yang tidak diinginkan. Teknik verifikasi formal dapat membantu Anda memeta

VUnit adalah salah satu kerangka kerja verifikasi VHDL open-source paling populer yang tersedia saat ini. Ini menggabungkan runner suite pengujian Python dengan pustaka VHDL khusus untuk mengotomatiskan bangku pengujian Anda. Untuk memberi Anda tutorial VUnit gratis ini, VHDLwhiz meminta Ahmadmun

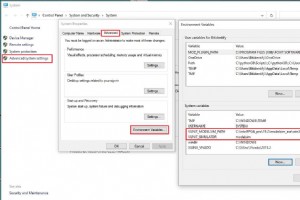

Pernahkah Anda ingin menjalankan simulasi VHDL yang menyertakan inti IP Quartus melalui kerangka kerja verifikasi VUnit? Itulah yang ada dalam pikiran insinyur FPGA Konstantinos Paraskevopoulos, tetapi dia tidak dapat menemukan tutorial yang cocok untuk itu. Untungnya, dia menggunakan bakatnya untu

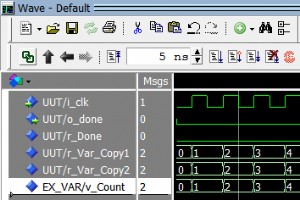

Variabel dalam VHDL bertindak mirip dengan variabel dalam C. Nilainya valid di lokasi yang tepat dalam kode di mana variabel dimodifikasi. Oleh karena itu, jika sinyal menggunakan nilai variabel sebelum tugas, itu akan memiliki nilai variabel lama. Jika sinyal menggunakan nilai variabel setelah tuga

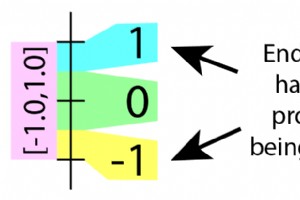

Semua Desainer Digital harus memahami cara kerja matematika di dalam FPGA atau ASIC. Langkah pertama untuk itu adalah memahami cara kerja jenis sinyal yang ditandatangani dan tidak ditandatangani. Jenis yang ditandatangani dan tidak ditandatangani ada di numeric_std paket, yang merupakan bagian dari

Konstruksi Record dalam VHDL dapat digunakan untuk menyederhanakan kode Anda. Catatan mirip dengan struktur di C . Rekaman paling sering digunakan untuk mendefinisikan tipe VHDL baru. Tipe baru ini berisi kelompok sinyal apa pun yang diinginkan pengguna. Paling sering ini digunakan untuk menyederhan

VHDL