Pentingnya Verifikasi Keandalan dalam Prosesor AI/ML

Dengan adopsi kecerdasan buatan dan pembelajaran mesin di berbagai aplikasi, verifikasi keandalan prosesor AI/ML sangat penting karena kegagalan dapat memiliki konsekuensi besar untuk validitas dan legitimasi teknologi AI/ML.

Dalam beberapa tahun terakhir, telah terjadi ekspansi pesat dalam jumlah perusahaan yang menerapkan kecerdasan buatan (AI) dan pembelajaran mesin (ML) dalam berbagai aplikasi. Faktanya, penelitian menunjukkan bahwa 2019 adalah tahun rekor bagi perusahaan yang mengadopsi AI dan ML, dan bahwa perusahaan-perusahaan ini menganggap kedua fitur ini sebagai yang paling dibutuhkan untuk mencapai strategi dan tujuan bisnis mereka. Adopsi yang berkembang ini terutama disebabkan oleh peningkatan algoritme, kemajuan dalam desain perangkat keras, dan peningkatan volume data yang dihasilkan oleh digitalisasi informasi.

Namun, untuk mendukung dan mempertahankan pertumbuhan AI/ML, perusahaan harus terus membuktikan kepada pasar bahwa hasil yang mereka peroleh dengan teknologi AI/ML dapat dipercaya. Kepercayaan itu dimulai dengan desain dan verifikasi sirkuit terpadu (IC) yang mendasari fungsionalitas AI/ML.

Klasifikasi AI dan ML

Pemrosesan AI dapat secara luas diklasifikasikan ke dalam pusat data/berbasis cloud atau tertanam, tergantung pada apakah itu dilakukan di situs cloud/pusat data, atau di sisi pengguna akhir (dengan menyematkan chip AI khusus atau mesin co-prosesor AI dengan sistem-on-chip (SOC) di dalam perangkat atau di tepi). Edge dalam konteks ini mengacu pada server lokal atau mesin yang lebih dekat ke perangkat daripada pusat data atau cloud.

Dalam hal aplikasi target, perangkat tepi dapat diklasifikasikan ke dalam pelatihan (ML) atau inferensi. Secara historis, porsi pelatihan diselesaikan di situs cloud, dengan porsi inferensi ditangani baik di cloud atau di perangkat edge. Dengan pengembangan solusi komputasi edge berkinerja tinggi yang baru, kami menyaksikan perubahan paradigma seiring semakin banyak aktivitas pelatihan yang dialihkan ke edge side.

Desain Chip AI/ML

Chip AI/ML dalam solusi komputasi tepi atau tertanam di dalam perangkat lokal dirancang untuk digunakan di lingkungan tertentu, seperti perusahaan, otomotif, industri, perawatan kesehatan, Internet of things (IoT), dll. Beberapa aplikasi ini sangat penting, artinya kegagalan apa pun dapat mengakibatkan konsekuensi bencana di dunia nyata. Misalnya, pertimbangkan sistem bantuan pengemudi tingkat lanjut (ADAS) yang digunakan di dalam mobil. Jika prosesor ADAS mengalami lebih dari latensi yang diberikan saat membaca data dari sensor dan menarik kesimpulan, hal itu dapat menyebabkan tabrakan.

IC yang digunakan dalam aplikasi AI/ML dicirikan oleh unit komputasi pemrosesan paralel yang besar, disipasi daya tinggi, dan sirkuit kompleks yang dapat memberikan kinerja maksimum dalam anggaran daya yang ketat. Sementara beberapa perusahaan menggunakan unit pemrosesan pusat (CPU) tradisional untuk tugas-tugas terkait AI, beberapa pakar industri berpendapat bahwa menggunakan CPU tidak terlalu efisien, karena sifat terdistribusi dari algoritme AI yang canggih. Algoritme ini memang memberikan solusi komputasi paralel dengan baik, seperti yang disediakan oleh unit pemrosesan grafis (GPU). Karena sifatnya yang dapat dikonfigurasi ulang, array gerbang yang dapat diprogram lapangan (FPGA) juga menarik minat untuk digunakan sebagai akselerator untuk chip AI.

ASIC dalam Aplikasi AI/ML

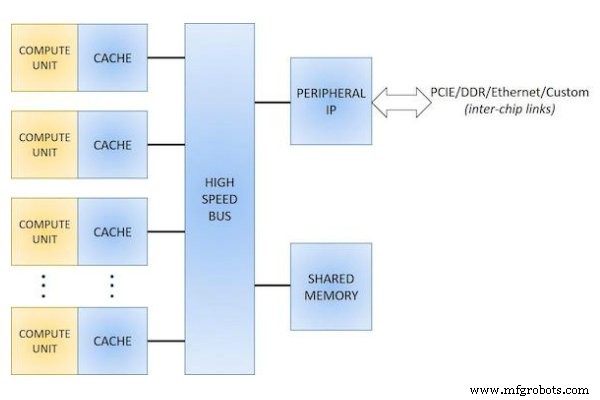

Secara keseluruhan, ada konsensus yang berkembang bahwa masalah rumit AI dan ML tidak memberikan solusi desain satu ukuran untuk semua. Untuk mengatasi masalah ini, banyak perusahaan mengembangkan IC khusus aplikasi (ASIC) mereka sendiri, yang mereka optimalkan bersama dengan tumpukan perangkat lunak untuk memberikan nilai terbaik untuk aplikasi AI/ML tertentu (Gambar 1).

Gambar 1. Blok diagram untuk desain chip AI ASIC.

Perusahaan-perusahaan ini mengklaim berbagai manfaat dari penggunaan ASIC ini, seperti kinerja yang lebih baik, lebih banyak operasi per siklus, desain yang lebih sederhana dan lebih deterministik dibandingkan dengan CPU atau GPU, penghematan area (karena pengecualian konstruksi dan mekanisme kompleks yang digunakan dalam a CPU), penggunaan daya yang lebih rendah, dan waktu pengembangan yang lebih cepat.

Komputasi Heterogen

Ada juga peningkatan dalam penggunaan komputasi heterogen—sistem yang menggunakan kombinasi berbagai tipe inti komputasi dalam upaya untuk menggabungkan kemampuan terbaik yang berbeda. Misalnya, dalam sistem yang menggunakan kombinasi CPU dan GPU, komputasi heterogen dapat bermanfaat dengan memindahkan tugas paralel ke GPU, sedangkan CPU menangani tugas seperti kontrol proses, yang sifatnya serial.

Salah satu aspek umum antara kelas prosesor AI yang berbeda adalah prosesor tersebut dioptimalkan untuk kinerja tinggi dan latensi rendah, sering kali menawarkan kinerja pengganda tera operasi per detik (TOPS). Untuk mendapatkan keunggulan di pasar yang sangat kompetitif ini, efisiensi daya (diukur dengan kinerja per watt) menjadi sama pentingnya dengan throughput mentah. Efisiensi daya sering dicapai dengan menggunakan kombinasi dari satu atau lebih teknik desain seperti power dan clock gating, tegangan dinamis dan penskalaan frekuensi, desain multi-Vt, dll.

Memastikan desain dan verifikasi yang andal dari IC kompleks ini sangat penting karena kegagalan sirkuit dalam chip ini dapat memiliki konsekuensi besar bagi validitas teknologi dan legitimasi hasil yang mereka berikan.

Verifikasi Keandalan IC AI/ML

Verifikasi keandalan merupakan tantangan besar dalam chip AI/ML, karena ukuran dan kompleksitas desain ini, dengan jumlah transistor dalam urutan jutaan — terkadang bahkan multi-miliar. Misalnya, GPU TESLA P100 NVIDIA menawarkan jumlah transistor yang mengejutkan sebesar 15,3 miliar, sementara IC Loihi Intel berisi 128 inti neuromorfik dan 3 inti X-86, dengan 2,07 miliar transistor. Dan, karena persyaratan keandalan untuk setiap lingkungan penggunaan berbeda, desainer harus memahami rangkaian persyaratan yang berlaku dan memastikan bahwa persyaratan tersebut dipenuhi dengan menguji desain mereka terhadap spesifikasi persyaratan keandalan yang ditetapkan dengan baik.

Metode Verifikasi Keandalan Desain

Secara tradisional, desainer menggunakan berbagai metode untuk memastikan keandalan desain, termasuk inspeksi manual dan teknik simulasi, terutama mengandalkan keahlian dan pengalaman tim desain mereka. Namun, inspeksi manual bukanlah pendekatan yang layak untuk chip AI/ML yang besar dan kompleks ini, karena memakan waktu dan rentan terhadap kesalahan manusia, dan hampir tidak mungkin untuk menyediakan cakupan yang memadai. Pendekatan simulasi seperti SPICE tradisional juga tidak praktis untuk IC ini, karena kurangnya skalabilitas untuk desain besar.

Untuk mengatasi masalah kapasitas dan runtime, banyak tim desain secara manual mempartisi desain dan memverifikasi blok kekayaan intelektual (IP) yang berbeda secara independen melalui simulasi atau alat tradisional. Namun, ada banyak interaksi antara blok IP yang berbeda dalam suatu desain (misalnya, antara inti komputasi yang berbeda dan bus atau tautan atau memori bandwidth tinggi), dan interaksi antar antarmuka sering kali cenderung diabaikan selama proses partisi manual. Alat verifikasi IC tradisional berjuang dengan waktu proses yang terlalu lama untuk memverifikasi desain yang rumit ini, seringkali membutuhkan waktu berhari-hari untuk memverifikasi desain yang besar, dan berpotensi menunda waktu untuk memasarkan.

Kekurangan dalam setiap proses ini menyoroti kebutuhan akan solusi otomatisasi desain elektronik (EDA) yang komprehensif yang dapat memanfaatkan kekuatan komputasi beberapa CPU dan perangkat secara bersamaan. Dengan verifikasi keandalan yang memenuhi syarat dan otomatis, tim desain dan verifikasi produk dapat lebih cepat berkumpul dalam verifikasi dan perbaikan keandalan, sehingga mengurangi waktu penyelesaian keseluruhan (TAT) mereka dari hari ke jam.

Platform Keandalan PERC Kaliber

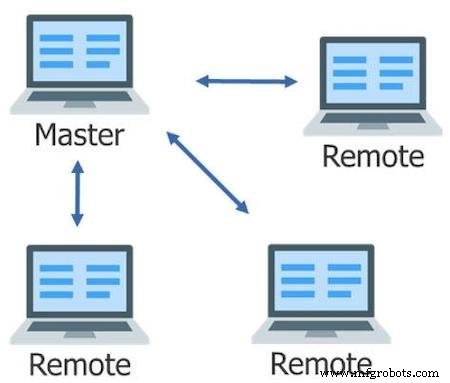

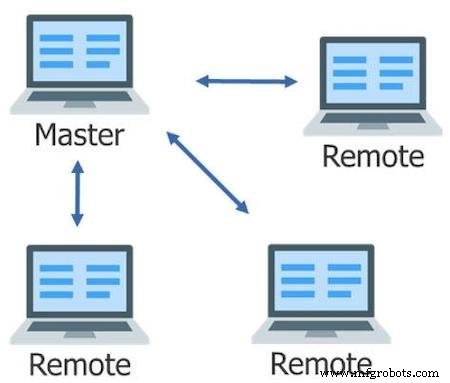

Selama beberapa tahun terakhir, kelas baru alat verifikasi keandalan IC yang menyelesaikan masalah proses ini telah muncul. Alat seperti platform keandalan Calibre™ PERC™ memanfaatkan serangkaian fitur dan fungsionalitas yang kaya untuk memberikan verifikasi keandalan yang cepat dan memenuhi syarat pengecoran. Misalnya, platform keandalan PERC Calibre memanfaatkan penskalaan multi-threaded (MT) dan multi-threaded flexible (MTflex) platform Calibre, yang mendistribusikan tugas ke beberapa CPU dan/atau mesin jarak jauh untuk menyediakan eksekusi proses verifikasi yang cepat dan efisien. pada chip besar dan kompleks seperti IC AI/ML (Gambar 2).

Gambar 2. Penskalaan multi-utas dan fleksibel mendistribusikan tugas ke beberapa remote untuk eksekusi keseluruhan yang lebih cepat.

Di luar mekanika dasar namun esensial ini, platform keandalan PERC Kaliber menyediakan pemrosesan inovatif yang menggabungkan informasi netlist dan tata letak dari sebuah desain untuk mengevaluasi berbagai potensi masalah keandalan dengan cepat dan tepat. Dengan memungkinkan desainer untuk secara efisien dan percaya diri mengurangi kerentanan desain terhadap kinerja dan kegagalan operasional, pendekatan verifikasi keandalan tingkat lanjut ini membantu mendukung pertumbuhan berkelanjutan dan adopsi teknologi AI/ML tepercaya.

Keandalan tingkat transistor

Sebagian besar desain ML/AI menggunakan beberapa domain daya untuk berbagai tujuan, seperti menyediakan catu daya yang bersih dan bebas noise untuk IP analog, memungkinkan kemampuan untuk membuka atau mematikan daya ke area chip tertentu, penskalaan tegangan naik atau turun secara independen untuk IP yang dipilih, atau memenuhi tuntutan arus tinggi menggunakan beberapa regulator tegangan. Misalnya, prosesor Skylake Intel berisi sembilan domain daya utama.

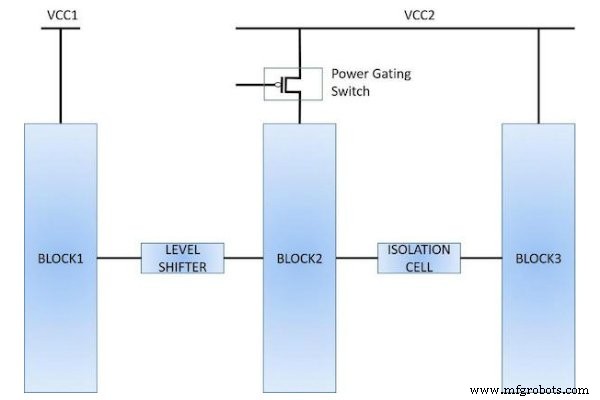

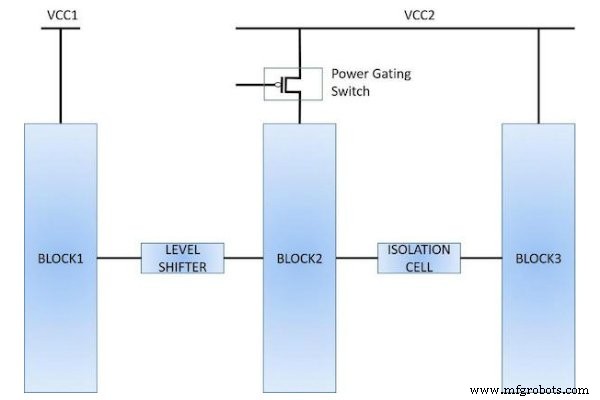

Menerapkan desain domain daya ganda memerlukan penggunaan elemen sirkuit khusus, seperti pengatur tegangan, sakelar header dan footer, pemindah level, sel isolasi, dan sel retensi status. Elemen-elemen ini menghadirkan serangkaian tantangan unik untuk verifikasi keandalan. Misalnya, perancang harus memverifikasi bahwa pemindah level atau sel isolasi yang sesuai digunakan pada setiap antarmuka domain dan bahwa mereka terhubung dengan benar (Gambar 3).

Gambar 3. Penggunaan elemen khusus (seperti pemindah level, sel isolasi, dan sakelar gerbang daya) di dalam desain daya rendah memerlukan teknik verifikasi khusus.

Mereka juga harus memastikan bahwa mereka menggunakan jenis perangkat yang sesuai pada domain daya yang berbeda, seperti perangkat oksida tebal untuk suplai tegangan tinggi. Memverifikasi kondisi ini membutuhkan pengetahuan dan proses yang sangat spesifik.

Teknik Format Daya Terpadu

Format daya terpadu (UPF) adalah teknik yang digunakan secara luas yang memungkinkan desainer menggunakan deskripsi yang konsisten tentang maksud daya di seluruh aliran desain. Namun, alur verifikasi berbasis UPF tradisional digunakan untuk memvalidasi IP pada tingkat logika atau gerbang, tetapi tidak memiliki kemampuan untuk memvalidasi implementasi tingkat transistor akhir, terutama sambungan sumur dan massal.

Platform keandalan PERC Kaliber dapat membaca file UPF untuk desain dan memanfaatkan informasi UPF untuk melakukan berbagai analisis pada level transistor, seperti mengidentifikasi pemindah level yang hilang atau tidak terhubung dengan benar, kondisi tegangan berlebih (EOS), sumur apung, dan banyak lagi . Dengan menggunakan platform keandalan PERC Kaliber bersama dengan data UPF, perancang dapat mengevaluasi interaksi perangkat secara terprogram untuk memberikan verifikasi keandalan yang berulang dan deterministik.

Keandalan Seumur Hidup dari AI/ML Chips

Keamanan operasional adalah aspek penting untuk sebagian besar chip AI/ML, yang diharapkan beroperasi sepanjang masa pakai yang dirancang tanpa gangguan atau kegagalan apa pun. Beberapa masalah keandalan listrik, seperti ketidakstabilan suhu bias (BTI) dan EOS, mungkin tidak bermanifestasi sebagai kegagalan langsung tetapi dapat menyebabkan degradasi dan penuaan yang cepat dari waktu ke waktu jika tidak diperbaiki sebelum diproduksi. Verifikasi keandalan dapat membantu memastikan operasi yang kuat selama periode yang diperpanjang dengan memeriksa berbagai masalah seperti resistensi titik-ke-titik, BTI positif dan negatif, kepadatan arus, dan elektromigrasi (EM), yang semuanya dapat menyebabkan penurunan kinerja atau kegagalan bencana.

Pertimbangkan kasus di mana perangkat domain tegangan tinggi menggerakkan perangkat oksida tipis yang tidak diberi peringkat untuk menangani tegangan tinggi. Selama desain, perancang gagal memasukkan shifter level tinggi-rendah. Meskipun kondisi ini tidak serta merta mempengaruhi fungsionalitas pada awalnya, ini akan membebani perangkat oksida tipis dari waktu ke waktu, yang pada akhirnya menyebabkan kegagalan. Waktu kegagalan yang sebenarnya tergantung pada nilai tegangan, waktu di mana suplai ON versus OFF, dan parameter proses.

EM (migrasi atom dalam konduktor karena arus listrik) adalah masalah besar lain yang mempengaruhi ketahanan jangka panjang dari interkoneksi yang digunakan dalam IC AI/ML. Migrasi ini menyebabkan void dan hillocks terbentuk pada kabel. Rongga menyebabkan peningkatan resistensi yang signifikan, sementara gundukan dapat membuat hubungan pendek, yang keduanya menyebabkan kegagalan sirkuit. Efek EM bergantung pada banyak faktor, seperti panjang dan lebar garis logam, bahan interkoneksi, suhu pengoperasian, arus satu arah vs. dua arah, dll.

Pengecoran memberi perusahaan desain batas EM untuk arus maksimum yang dapat ditangani kabel, berdasarkan kondisi penggunaan yang diharapkan untuk produk. Misalnya, batas EM untuk IC yang digunakan di dalam ponsel akan jauh lebih rendah daripada IC yang digunakan di lingkungan industri. Beberapa perusahaan memiliki tim khusus yang secara aktif terlibat dengan pengecoran untuk menentukan spesifikasi yang sesuai, membuat struktur pengujian, dan melakukan kualifikasi produk untuk toleransi EM. Jelas, lebih sulit untuk menentukan batasan ini untuk produk yang dapat digunakan di banyak lingkungan, jadi desainer biasanya merancang chip ini untuk kondisi operasi kasus terburuk. Dalam semua kasus, sangat penting untuk menguji desain terhadap batas EM yang ditentukan pengecoran dan memvalidasi bahwa desain dapat menahan efek EM.

Kegagalan untuk menangkap dan memperbaiki masalah keandalan yang berbeda selama fase verifikasi pra-silikon dapat mengakibatkan berbagai dampak, termasuk beberapa putaran tape-out, keterlambatan dalam memasarkan produk, hilangnya kepercayaan pelanggan, reaksi pasar negatif yang signifikan, penarikan produk, dan bahkan konsekuensi bencana, seperti cedera fisik atau hilangnya nyawa. Mengidentifikasi dan memperbaiki pelanggaran keandalan sebelum tape-out meminimalkan kemungkinan malfungsi atau kegagalan sirkuit yang terbukti memakan biaya.

Analisis dan Manajemen Keandalan AI/ML Sangat Penting

Keberhasilan dan perluasan baru-baru ini dalam fungsionalitas AI/ML sebagian besar didasarkan pada kemajuan teknologi semikonduktor. Saat desain baru ini dikembangkan, komunitas desain perangkat keras harus menyadari kebutuhan untuk menganalisis dan mengelola aspek keandalan desain, seperti lingkungan target, kondisi pengoperasian, kriteria keandalan, dll. Alat verifikasi keandalan EDA canggih yang dirancang untuk mengatasi masalah keandalan khusus dan persyaratan chip yang besar dan kompleks ini dapat membantu rumah desain memastikan bahwa produk mereka berfungsi sebagaimana dimaksud selama masa pakai yang dirancang. Pada gilirannya, itu berarti kepercayaan pada hasil yang dicapai melalui penggunaan aplikasi AI/ML di pasar yang lebih luas, mendukung penggunaan dan perluasannya secara berkelanjutan.

Artikel Industri adalah bentuk konten yang memungkinkan mitra industri untuk berbagi berita, pesan, dan teknologi yang bermanfaat dengan pembaca All About Circuits dengan cara yang tidak sesuai dengan konten editorial. Semua Artikel Industri tunduk pada pedoman editorial yang ketat dengan tujuan menawarkan kepada pembaca berita, keahlian teknis, atau cerita yang bermanfaat. Sudut pandang dan pendapat yang diungkapkan dalam Artikel Industri adalah dari mitra dan belum tentu dari All About Circuits atau penulisnya.