Verilog

Sebuah always blok adalah salah satu prosedur blok di Verilog. Pernyataan di dalam blok selalu dieksekusi secara berurutan.

always @ (event)

[statement]

always @ (event) begin

[multiple statements]

end

always blok dieksekusi pada beberapa acara tertentu. Acara ditentukan oleh daftar sensitivitas.

Sensitivitas list adalah ekspresi yang menentukan kapan blok selalu harus dieksekusi dan ditentukan setelah @ operator dalam tanda kurung ( ) . Daftar ini mungkin berisi satu atau sekelompok sinyal yang perubahan nilainya akan mengeksekusi blok always.

Pada kode di bawah ini, semua pernyataan di dalam always blok dieksekusi setiap kali nilai sinyal a atau b berubah.

// Execute always block whenever value of "a" or "b" change

always @ (a or b) begin

[statements]

end

Sebuah always blok dapat digunakan untuk mewujudkan elemen kombinasional atau berurutan. Elemen sekuensial seperti flip flop menjadi aktif ketika dilengkapi dengan jam dan reset. Demikian pula, blok kombinasional menjadi aktif ketika salah satu nilai inputnya berubah. Semua blok perangkat keras ini bekerja secara bersamaan secara independen satu sama lain. Hubungan antara masing-masing inilah yang menentukan aliran data. Untuk memodelkan perilaku ini, sebuah always blok dibuat sebagai proses berkelanjutan yang dipicu dan melakukan beberapa tindakan saat sinyal dalam daftar sensitivitas menjadi aktif.

Dalam contoh berikut, semua pernyataan dalam blok selalu dieksekusi di setiap sisi positif dari sinyal clk.

// Execute always block at positive edge of signal "clk"

always @ (posedge clk) begin

[statements]

end

always blok berulang terus menerus sepanjang durasi simulasi. Daftar sensitivitas membawa rasa waktu tertentu yaitu setiap kali ada sinyal dalam daftar sensitivitas berubah, blok selalu dipicu. Jika tidak ada pernyataan kontrol waktu dalam blok always, simulasi akan hang karena loop tak terbatas tanpa penundaan !

Contoh yang ditunjukkan di bawah ini adalah selalu blok yang mencoba untuk membalikkan nilai clk sinyal. Pernyataan dijalankan setelah setiap 0 unit waktu. Oleh karena itu, ia dieksekusi selamanya karena tidak adanya penundaan dalam pernyataan tersebut.

// always block is started at time 0 units

// But when is it supposed to be repeated ?

// There is no time control, and hence it will stay and

// be repeated at 0 time units only. This continues

// in a loop and simulation will hang !

always clk = ~clk;

Bahkan jika daftar sensitivitas kosong, harus ada beberapa bentuk lain dari penundaan waktu. Waktu simulasi dimajukan oleh pernyataan penundaan dalam always membangun seperti yang ditunjukkan di bawah ini. Sekarang, pembalikan jam dilakukan setelah setiap 10 satuan waktu.

always #10 clk = ~clk;

Catatan: Penundaan eksplisit tidak dapat disintesis menjadi gerbang logika !

Karenanya kode desain Verilog yang asli selalu memerlukan daftar sensitivitas.

Kode yang ditunjukkan di bawah ini mendefinisikan modul yang disebut tff yang menerima input data, jam, dan reset aktif-rendah. Output akan terbalik setiap kali d ditemukan menjadi 1 di tepi positif jam. Di sini, always blok dipicu baik di tepi positif clk atau tepi negatif rstn.

Peristiwa berikut terjadi di tepi positif jam dan diulang untuk semua tepi positif jam.

if pertama blokir cek nilai reset aktif-rendah rstn

module tff (input d,

clk,

rstn,

output reg q);

always @ (posedge clk or negedge rstn) begin

if (!rstn)

q <= 0;

else

if (d)

q <= ~q;

else

q <= q;

end

endmodule

Peristiwa berikut terjadi pada tepi negatif pertama dan terjadi pada semua kejadian tersebut.

if pertama blok memeriksa nilai rstn reset aktif-rendah. Di tepi negatif sinyal, nilainya adalah 0.

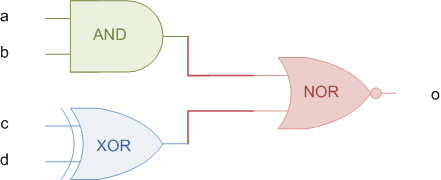

Sebuah always blok juga dapat digunakan dalam desain blok kombinasional. Misalnya rangkaian digital berikut mewakili kombinasi dari tiga gerbang logika berbeda yang memberikan keluaran tertentu pada sinyal o.

Kode di bawah ini adalah module dengan empat port input dan satu port output yang disebut o. always blok dipicu setiap kali salah satu sinyal dalam daftar sensitivitas berubah nilainya. Sinyal keluaran dideklarasikan sebagai tipe reg dalam daftar port modul karena digunakan dalam blok prosedural. Semua sinyal yang digunakan dalam blok prosedural harus dideklarasikan sebagai tipe reg .

module combo ( input a,

input b,

input c,

input d,

output reg o);

always @ (a or b or c or d) begin

o <= ~((a & b) | (c^d));

end

endmodule

Lihat bahwa sinyal o menjadi 1 setiap kali ekspresi kombinasional pada RHS menjadi benar. Demikian pula o menjadi 0 ketika RHS salah.

Keluaran SimulasiKlik di sini untuk slideshow dengan contoh simulasi !

Verilog

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang

Desain module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else