Verilog

Penjumlah adalah komponen digital yang melakukan penambahan dua angka. Ini adalah komponen utama di dalam ALU prosesor dan digunakan untuk menambah alamat, indeks tabel, pointer buffer, dan di banyak tempat lain di mana penambahan diperlukan.

Sebuah penambah penuh menambahkan input carry bersama dengan bilangan biner input lainnya untuk menghasilkan jumlah dan output carry.

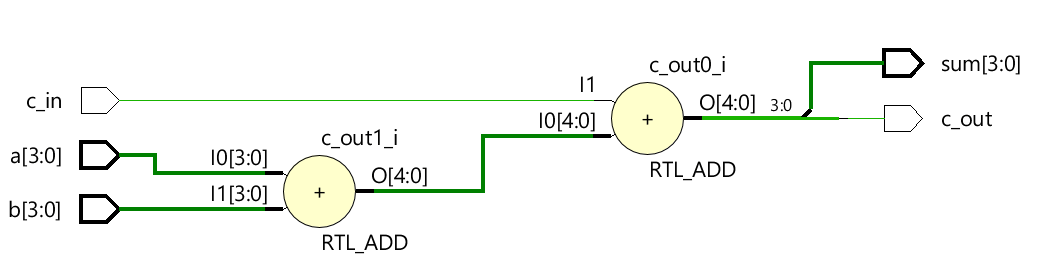

Contoh penambah 4-bit ditunjukkan di bawah ini yang menerima dua bilangan biner melalui sinyal a dan b yang keduanya lebar 4-bit. Karena penambah adalah rangkaian kombinasional, penambah dapat dimodelkan di Verilog menggunakan penugasan berkelanjutan dengan assign atau always blok dengan daftar sensitivitas yang terdiri dari semua input. Kode yang ditunjukkan di bawah ini adalah kode dari pendekatan sebelumnya.

module fulladd ( input [3:0] a,

input [3:0] b,

input c_in,

output c_out,

output [3:0] sum);

assign {c_out, sum} = a + b + c_in;

endmodule

Kode yang ditunjukkan di bawah ini menggunakan always blok yang dieksekusi setiap kali inputnya mengubah nilai.

module fulladd ( input [3:0] a,

input [3:0] b,

input c_in,

output reg c_out,

output reg [3:0] sum);

always @ (a or b or c_in) begin

{c_out, sum} = a + b + c_in;

end

endmodule

module tb_fulladd;

// 1. Declare testbench variables

reg [3:0] a;

reg [3:0] b;

reg c_in;

wire [3:0] sum;

integer i;

// 2. Instantiate the design and connect to testbench variables

fulladd fa0 ( .a (a),

.b (b),

.c_in (c_in),

.c_out (c_out),

.sum (sum));

// 3. Provide stimulus to test the design

initial begin

a <= 0;

b <= 0;

c_in <= 0;

$monitor ("a=0x%0h b=0x%0h c_in=0x%0h c_out=0x%0h sum=0x%0h", a, b, c_in, c_out, sum);

// Use a for loop to apply random values to the input

for (i = 0; i < 5; i = i+1) begin

#10 a <= $random;

b <= $random;

c_in <= $random;

end

end

endmodule

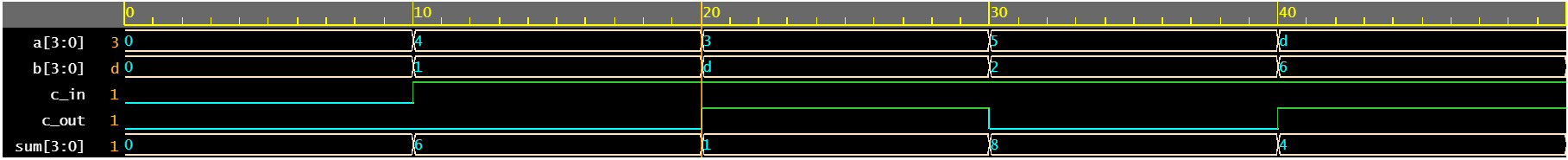

Perhatikan bahwa ketika a dan b dijumlahkan untuk menghasilkan angka yang lebarnya lebih dari 4 bit, jumlah akan digulung ke nol dan c_out menjadi 1. Misalnya, garis yang disorot dengan warna kuning dijumlahkan menjadi 0x11 dan 4 bit yang lebih rendah ditugaskan ke jumlah dan bit#4 ke c_out.

Log Simulasincsim> run a=0x0 b=0x0 c_in=0x0 c_out=0x0 sum=0x0 a=0x4 b=0x1 c_in=0x1 c_out=0x0 sum=0x6 a=0x3 b=0xd c_in=0x1 c_out=0x1 sum=0x1 a=0x5 b=0x2 c_in=0x1 c_out=0x0 sum=0x8 a=0xd b=0x6 c_in=0x1 c_out=0x1 sum=0x4 a=0xd b=0xc c_in=0x1 c_out=0x1 sum=0xa ncsim: *W,RNQUIE: Simulation is complete.

Verilog

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang

Desain module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else

Penjumlah adalah komponen digital yang melakukan penambahan dua angka. Ini adalah komponen utama di dalam ALU prosesor dan digunakan untuk menambah alamat, indeks tabel, pointer buffer, dan di banyak tempat lain di mana penambahan diperlukan. Sebuah penambah penuh menambahkan input carry bersama de