Tertanam

Lihat seri Terungkap RTOS Artikel ini melanjutkan pembahasan tentang semaphore. Layanan Utilitas Semaphore Nucleus RTOS memiliki empat panggilan API yang menyediakan fungsi utilitas yang terkait dengan semaphore:reset semaphore, mengembalikan informasi tentang semaphore, mengembalikan nomor semap

Lihat seri Terungkap RTOS Kotak surat diperkenalkan di artikel sebelumnya. Mereka mungkin merupakan metode komunikasi antar-tugas kedua yang paling sederhana – setelah sinyal – yang didukung oleh Nucleus SE. Mereka menyediakan sarana berbiaya rendah, tetapi fleksibel, untuk menyampaikan pesan sede

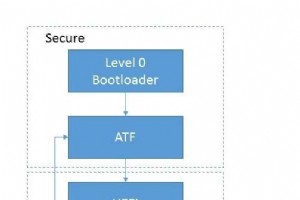

Sejak dirilis pada tahun 2011, arsitektur prosesor ARMv8 telah menjadi cukup luas di pasar perangkat seluler. Menurut perkiraan CEO ARM Limited, prosesor generasi ini akan memperoleh pangsa pasar dunia hingga 25% pada tahun 2020. Wajar jika dukungan perangkat lunak didirikan dan telah berkembang leb

Catatan editor:Teman baik kami Max sedang mencari saran untuk kalkulator dan pemecah elektronik. Tidak ada yang terlalu besar atau terlalu kecil. Beri tahu dia yang menurut Anda layak untuk dimasukkan dalam daftar alat EEWeb.com. Sesekali, sinar matahari yang tak terduga menerobos awan untuk menc

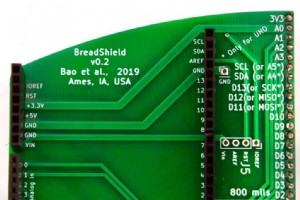

Saya menerima email dalam jumlah yang luar biasa dari orang-orang yang telah meluncurkan kampanye crowdfunding untuk berbagai proyek. Ini mungkin karena saya sendiri kadang-kadang mencelupkan kaki saya ke dalam air crowdfunding, ditambah fakta bahwa saya telah memposting beberapa kolom pada proyek y

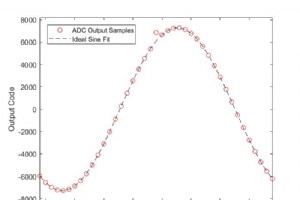

Karena konverter analog-ke-digital (ADC) berkecepatan tinggi telah meningkat dalam laju pengambilan sampel, demikian juga masalah kesalahan kode — juga dikenal sebagai kode kilau — dalam data keluaran ADC. Kesalahan kode didefinisikan sebagai kesalahan dalam kode keluaran ADC yang melebihi ambang ba

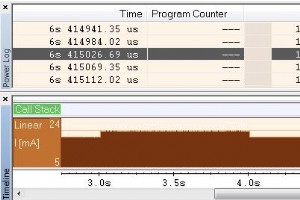

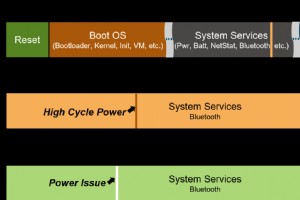

Dalam posting terakhir saya, “Dasar-dasar mode daya rendah Arm Cortex-M”, kami menjelajahi dasar-dasar mode daya rendah yang dapat ditemukan di setiap prosesor Arm Cortex-M dan bagaimana kami dapat memanfaatkan instruksi WFI dan WFE untuk menempatkan prosesor tidur. Pertanyaan yang benar-benar tersi

Listrik cenderung membutuhkan biaya; biaya listrik yang tinggi sangat mahal. Adaptasi yang agak dipaksakan dari kutipan terkenal Lord Acton ini menangkap dua aspek penting dari desain semikonduktor dan konsumsi daya. Melihat konsumsi daya rata-rata dari waktu ke waktu, jelas bahwa chip dengan konsum

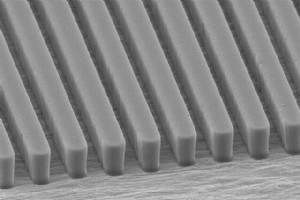

Dalam beberapa tahun terakhir, kami telah melihat perkembangan aplikasi elektronik baru yang membutuhkan paket yang lebih kecil, faktor bentuk baru, konsumsi daya yang lebih rendah, dan peningkatan fungsionalitas termasuk pemrosesan sinyal yang disematkan, sensor, antarmuka pencitraan, dan komponen

Sejak awal desain elektronik, di mana ada desain, ada bug. Tapi di mana mereka memiliki bug, pasti ada debug, terlibat dalam pertandingan gulat epik dengan kesalahan, bug, dan kesalahan untuk menentukan mana yang akan menang — dan seberapa teliti. Dalam banyak hal, evolusi teknologi debug sama mena

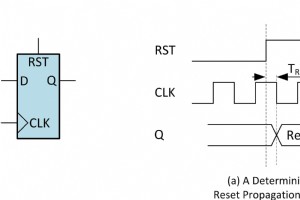

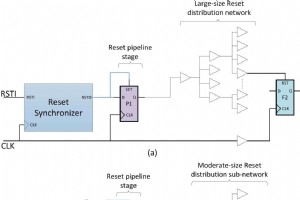

Kurangnya koordinasi antara reset asinkron dan jam logika sinkron menyebabkan kegagalan intermiten pada penyalaan. Dalam rangkaian artikel ini, kami membahas persyaratan dan tantangan reset asinkron dan mengeksplorasi solusi lanjutan untuk desain ASIC vs FPGA. Reset asinkron secara tradisional digu

Kurangnya koordinasi antara reset asinkron dan jam logika sinkron menyebabkan kegagalan intermiten pada penyalaan. Dalam rangkaian artikel ini, kami membahas persyaratan dan tantangan reset asinkron dan mengeksplorasi solusi lanjutan untuk desain ASIC vs FPGA. Reset asinkron secara tradisional digu

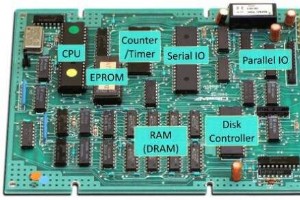

Ada banyak Sistem Operasi Waktu Nyata (RTOS) yang tersedia di Internet (Klik di Sini untuk melihat daftar kecil). Namun, banyak dari penawaran ini sekarang menjadi proyek mati/tidak terawat. Dari yang tersisa, sebagian besar hanya mendukung satu mikrokontroler atau satu keluarga mikrokontroler. Mem

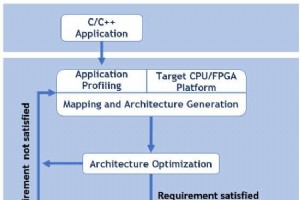

Baru-baru ini, Brian Bailey mengorganisir meja bundar yang menghasilkan artikel dua bagian yang disebut Mendukung CPU Plus FPGA . Para ahli membahas realitas yang berkembang dari desain sistem berdasarkan FPGA dan CPU. Diskusi ini membahas perkembangan terkini dalam alur desain dan bagaimana penggun

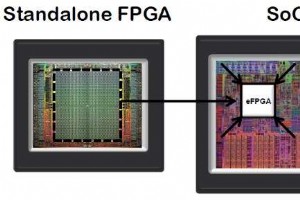

Saya sudah lama tertarik dengan teknologi yang keluar dari Achronix. Mereka pertama kali menarik minat saya sekitar tahun 2004/2005 dengan kain FPGA asinkron mereka. Akhirnya, ini berhasil mencapai kecepatan yang setara dengan FPGA sinkron yang di-clock pada 2 GHz (jika ada monster seperti itu), tet

Earbud stereo yang dapat didengar dan benar-benar nirkabel semakin populer, tetapi masih jauh dari mencapai potensi penuhnya. Perangkat kecil ini dapat mengubah cara orang berinteraksi dengan lingkungan mereka, menambahkan kemampuan pendengaran yang ditingkatkan, kenikmatan, dan keamanan dalam kehid

Catatan Editor:Desain nirkabel dapat menghalangi rencana terbaik untuk pengembangan perangkat yang terhubung. Secara khusus, feedline antena yang dirancang dengan tidak benar mungkin sulit ditemukan hingga pengembangannya terlambat selama pengujian. Berikut adalah artikel yang bagus dari teman-teman

Selama beberapa tahun terakhir, kemajuan signifikan dalam pengenalan ucapan otomatis (ASR) telah menyebabkan banyak perangkat dan aplikasi yang menggunakan ucapan sebagai antarmuka utama mereka. Spektrum IEEE majalah telah mendeklarasikan 2017 sebagai tahun pengenalan suara; ZDNet melaporkan dari CE

Selama karir saya, saya telah terlibat dengan mengembangkan sejumlah desain FPGA untuk beberapa proyek yang sangat menarik. Sayangnya, saya juga terlibat dalam menyelamatkan beberapa desain FPGA yang telah tersesat. Saat saya mengerjakan desain masalah ini, menjadi jelas bahwa — meskipun aplikasi ta

Istilah 5G — yang berarti jaringan seluler atau sistem nirkabel generasi kelima — semakin banyak muncul akhir-akhir ini. Ada pembicaraan tentang penerapan awal pada awal tahun 2020. Yang kurang dibicarakan adalah fakta bahwa standar 5G masih dipertimbangkan dan ditetapkan, dan banyak aspek yang masi

Tertanam