Tugas sistem tampilan terutama digunakan untuk menampilkan pesan informasi dan debug untuk melacak aliran simulasi dari file log dan juga membantu debug lebih cepat. Ada kelompok tugas dan format tampilan yang berbeda di mana mereka dapat mencetak nilai. Tampilkan/Tulis Tugas Sintaks Keduanya $dis

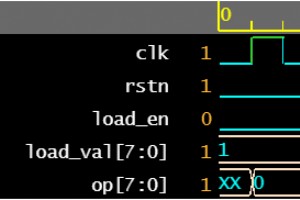

Jam sangat penting untuk membangun sirkuit digital karena memungkinkan blok yang berbeda sinkron satu sama lain. Properti jam Properti utama dari jam digital adalah frekuensi yang menentukan periode jam , siklus tugasnya dan fase jam dalam kaitannya dengan jam lainnya. Periode Jam Frekuensi menunj

Desain Verilog dan testbench biasanya memiliki banyak baris kode yang terdiri dari always atau initial blok, penugasan berkelanjutan, dan pernyataan prosedural lainnya yang menjadi aktif pada waktu yang berbeda selama simulasi. Setiap perubahan nilai sinyal dalam model Verilog dianggap sebagai peri

Simulasi Verilog tergantung pada bagaimana waktu didefinisikan karena simulator perlu mengetahui apa arti #1 dalam hal waktu. `timescale direktif compiler menentukan unit waktu dan presisi untuk modul yang mengikutinya. Sintaks `timescale <time_unit>/<time_precision> // Example `ti

Verilog adalah bahasa deskripsi perangkat keras dan tidak ada persyaratan bagi desainer untuk mensimulasikan desain RTL mereka agar dapat mengubahnya menjadi gerbang logika. Jadi apa yang perlu disimulasikan? Simulasi adalah teknik menerapkan stimulus input yang berbeda ke desain pada waktu yang

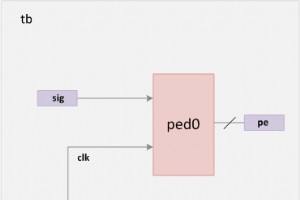

Primitif Verilog standar seperti nand dan not mungkin tidak selalu mudah atau cukup untuk mewakili logika yang kompleks. Elemen primitif baru yang disebut UDP atau primitif yang ditentukan pengguna dapat didefinisikan untuk memodelkan logika kombinasional atau sekuensial. Semua UDP memiliki tepat s

Verilog juga menyediakan dukungan untuk pemodelan level transistor meskipun jarang digunakan oleh desainer akhir-akhir ini karena kompleksitas sirkuit mengharuskan mereka untuk pindah ke level abstraksi yang lebih tinggi daripada menggunakan pemodelan level sakelar. NMOS/PMOS module des (input

Elemen digital adalah entitas biner dan hanya dapat menampung salah satu dari dua nilai - 0 dan 1. Namun transisi dari 0 ke 1 dan 1 ke 0 memiliki penundaan transisi dan begitu juga setiap elemen gerbang untuk menyebarkan nilai dari input ke outputnya. Misalnya, gerbang AND dua input harus mengalih

Beberapa primitif bawaan utama telah dibahas dalam artikel sebelumnya dan akan lebih baik untuk melihat beberapa contoh praktis menggunakan and sederhana , nor dan not gerbang. Perhatikan bahwa untuk menulis kode Verilog menggunakan gerbang, Anda perlu mengetahui cara menghubungkan elemen. Ini sang

Sebagian besar desain digital dilakukan pada tingkat abstraksi yang lebih tinggi seperti RTL, meskipun terkadang menjadi intuitif untuk membangun sirkuit deterministik yang lebih kecil pada tingkat yang lebih rendah dengan menggunakan elemen kombinasional seperti dan dan atau . Pemodelan yang dilaku

Sebagian besar bahasa pemrograman memiliki fitur karakteristik yang disebut lingkup yang mendefinisikan visibilitas bagian kode tertentu ke variabel dan metode. Lingkup mendefinisikan namespace untuk menghindari tabrakan antara nama objek yang berbeda dalam namespace yang sama. Verilog mendefinisik

Pernyataan penundaan Verilog dapat memiliki penundaan yang ditentukan baik di sisi kiri atau sisi kanan operator penugasan. Penundaan Antar-tugas // Delay is specified on the left side #<delay> <LHS> = <RHS> Sebuah antar-tugas pernyataan delay memiliki nilai delay pada LHS

Ada dua jenis kontrol waktu di Verilog - delay dan acara ekspresi. penundaan control hanyalah cara menambahkan penundaan antara waktu simulator menemukan pernyataan dan ketika itu benar-benar dijalankan. Ekspresi peristiwa memungkinkan pernyataan ditunda sampai terjadinya beberapa peristiwa simulasi

Verilog mendukung beberapa arahan kompiler yang pada dasarnya mengarahkan kompiler untuk memperlakukan kode dengan cara tertentu. Misalnya, sebagian kode dapat mewakili implementasi fitur tertentu dan harus ada cara untuk tidak menyertakan kode dalam desain jika fitur tersebut tidak digunakan. Ini

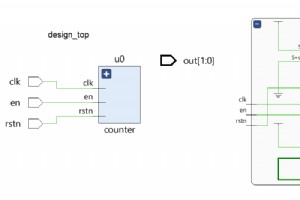

Parameter adalah konstruksi Verilog yang memungkinkan modul untuk digunakan kembali dengan spesifikasi yang berbeda. Misalnya, penambah 4-bit dapat diparameterisasi untuk menerima nilai jumlah bit dan nilai parameter baru dapat diteruskan selama pembuatan modul. Jadi, penambah N-bit bisa menjadi pen

Sebuah function dimaksudkan untuk melakukan beberapa pemrosesan pada input dan mengembalikan nilai tunggal, sedangkan task lebih umum dan dapat menghitung beberapa nilai hasil dan mengembalikannya menggunakan keluaran dan keluar ketik argumen. Tugas dapat berisi elemen simulasi yang memakan waktu se

Sering kali kami menemukan potongan kode tertentu berulang dan dipanggil beberapa kali dalam RTL. Mereka kebanyakan tidak mengkonsumsi waktu simulasi dan mungkin melibatkan perhitungan kompleks yang perlu dilakukan dengan nilai data yang berbeda. Dalam kasus seperti itu, kita dapat mendeklarasikan f

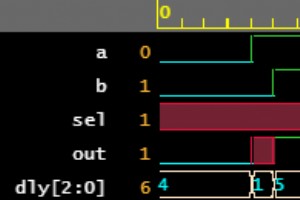

case pernyataan memeriksa apakah ekspresi yang diberikan cocok dengan salah satu ekspresi lain dalam daftar dan bercabang sesuai. Biasanya digunakan untuk mengimplementasikan multiplexer. Konstruksi if-else mungkin tidak cocok jika ada banyak kondisi yang harus diperiksa dan akan disintesis menjadi

Sebuah for loop adalah loop yang paling banyak digunakan dalam perangkat lunak, tetapi terutama digunakan untuk mereplikasi logika perangkat keras di Verilog. Ide di balik for loop adalah untuk mengulangi satu set pernyataan yang diberikan dalam loop selama kondisi yang diberikan benar. Ini sangat m

Perilaku perangkat keras tidak dapat diimplementasikan tanpa pernyataan bersyarat dan cara lain untuk mengontrol aliran logika. Verilog memiliki serangkaian blok aliran kontrol dan mekanisme untuk mencapai hal yang sama. jika-lain-jika pernyataan bersyarat . ini digunakan untuk membuat keputusan te

Verilog