Memblokir Memblokir pernyataan penugasan ditugaskan menggunakan = dan dieksekusi satu demi satu dalam blok prosedural. Namun, ini tidak akan mencegah eksekusi pernyataan yang berjalan di blok paralel. module tb; reg [7:0] a, b, c, d, e; initial begin a = 8hDA; $display ([%0t] a=

Menempatkan nilai ke jaring dan variabel disebut penugasan. Ada tiga bentuk dasar: Prosedur Berkelanjutan Prosedural berkelanjutan Nilai LHS legal Tugas memiliki dua bagian - sisi kanan (RHS) dan sisi kiri (LHS) dengan simbol sama dengan (=) atau simbol kurang dari sama (<=) di antaranya. Jenis

Ada beberapa cara untuk mengelompokkan sekumpulan pernyataan bersama-sama yang secara sintaksis setara dengan satu pernyataan dan dikenal sebagai pernyataan blok . Ada dua jenis pernyataan blok:berurutan dan paralel. Sequential Pernyataan dibungkus menggunakan begin dan end kata kunci dan akan diek

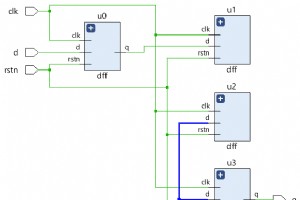

Contoh sebelumnya mengeksplorasi detektor urutan sederhana. Berikut adalah contoh lain untuk pendeteksi pola yang mendeteksi pola yang sedikit lebih panjang. Desain module det_110101 ( input clk, input rstn, input in, output out );

Contoh yang sangat umum dari FSM adalah detektor urutan di mana desain perangkat keras diharapkan untuk mendeteksi ketika pola tetap terlihat dalam aliran bit biner yang dimasukkan ke dalamnya. Contoh module det_1011 ( input clk, input rstn, input in,

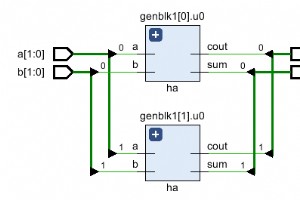

Sebuah generate block memungkinkan untuk menggandakan instance modul atau melakukan instantiasi bersyarat dari modul apa pun. Ini memberikan kemampuan untuk desain yang akan dibangun berdasarkan parameter Verilog. Pernyataan ini sangat cocok ketika operasi yang sama atau contoh modul perlu diulang b

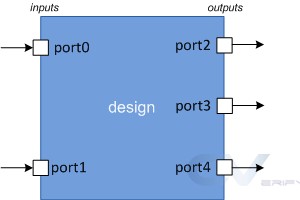

Semua kode perilaku ditulis di dalam module dan endmodule . Jadi, desain digital apa pun yang ingin Anda buat, itu akan masuk ke dalam module memblokir. Mungkin atau mungkin tidak memiliki port yang ditentukan - izinkan sinyal masuk ke blok sebagai input atau keluar dari blok sebagai output . Modul

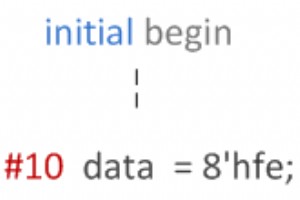

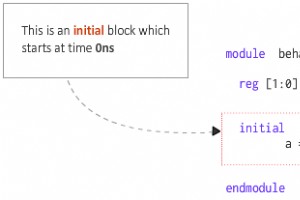

Satu set pernyataan Verilog biasanya dieksekusi secara berurutan dalam simulasi. Pernyataan ini ditempatkan di dalam prosedur memblokir. Terutama ada dua jenis prosedur blok di Verilog - awal dan selalu Sintaks initial [single statement] initial begin [multiple statements] end Untu

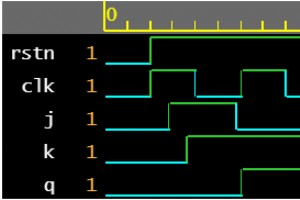

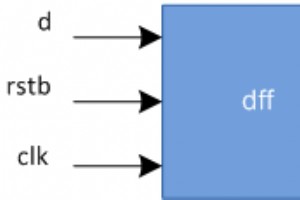

Artikel sebelumnya menunjukkan berbagai contoh penggunaan always blok untuk mengimplementasikan logika kombinasional. Sebuah always blok juga terutama digunakan untuk mengimplementasikan sequential logika yang memiliki elemen memori seperti sandal jepit yang dapat menyimpan nilai. JK Flip Flop Flip

Verilog selalu memblokir dapat digunakan untuk logika sekuensial dan kombinasional. Beberapa contoh desain ditampilkan menggunakan assign pernyataan di artikel sebelumnya. Kumpulan desain yang sama akan dieksplorasi selanjutnya menggunakan always blokir. Contoh #1 :Logika kombinasional sederhana Ko

Sebuah always blok adalah salah satu prosedur blok di Verilog. Pernyataan di dalam blok selalu dieksekusi secara berurutan. Sintaks always @ (event) [statement] always @ (event) begin [multiple statements] end always blok dieksekusi pada beberapa acara tertentu. Acara ditentukan oleh da

Kabel dan variabel Verilog multi-bit dapat disatukan untuk membentuk kabel atau variabel multi-net yang lebih besar menggunakan penggabungan operator { dan } dipisahkan dengan koma. Penggabungan juga diperbolehkan memiliki ekspresi dan konstanta berukuran sebagai operan selain kabel dan variabel. U

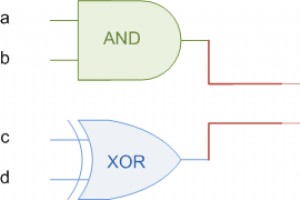

Data yang tidak dapat diproses sangat tidak berguna, akan selalu ada beberapa bentuk perhitungan yang diperlukan dalam rangkaian digital dan sistem komputer. Mari kita lihat beberapa operator di Verilog yang memungkinkan alat sintesis mewujudkan elemen perangkat keras yang sesuai. Operator Aritmatik

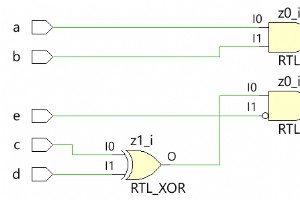

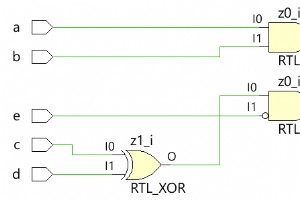

Pernyataan penetapan verilog biasanya digunakan untuk terus menggerakkan sinyal wire tipe data dan disintesis sebagai logika kombinasional. Berikut adalah beberapa contoh desain lainnya menggunakan assign pernyataan. Contoh #1 :Logika kombinasional sederhana Kode yang ditunjukkan di bawah ini mengi

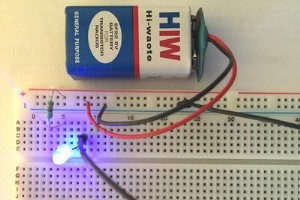

Sinyal tipe wire atau kabel serupa seperti tipe data memerlukan penetapan nilai yang berkelanjutan. Misalnya, pertimbangkan kabel listrik yang digunakan untuk menghubungkan potongan-potongan pada papan tempat memotong roti. Selama baterai +5V diterapkan ke salah satu ujung kabel, komponen yang terhu

Seperti yang kita lihat di artikel sebelumnya, desain yang lebih besar dan kompleks dibangun dengan mengintegrasikan beberapa modul secara hierarkis. Modul dapat dibuat instance dalam modul dan port lain dari instance ini dapat dihubungkan dengan sinyal lain di dalam modul induk. Koneksi port ini d

Port adalah seperangkat sinyal yang bertindak sebagai input dan output ke modul tertentu dan merupakan cara utama untuk berkomunikasi dengannya. Pikirkan modul sebagai chip buatan yang ditempatkan pada PCB dan menjadi sangat jelas bahwa satu-satunya cara untuk berkomunikasi dengan chip adalah melalu

Sebuah module adalah blok kode Verilog yang mengimplementasikan fungsi tertentu. Modul dapat disematkan di dalam modul lain dan modul tingkat yang lebih tinggi dapat berkomunikasi dengan modul tingkat yang lebih rendah menggunakan port input dan outputnya. Sintaks Sebuah modul harus diapit dalam mo

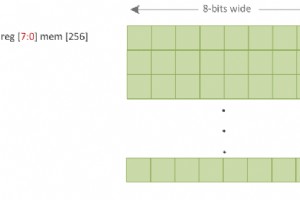

Sebuah array deklarasi jaring atau variabel dapat berupa skalar atau vektor. Sejumlah dimensi dapat dibuat dengan menentukan rentang alamat setelah nama pengenal dan disebut array multi-dimensi. Array diperbolehkan di Verilog untuk reg , wire , integer dan real tipe data. reg y1 [11:0]

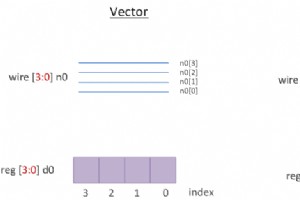

Verilog perlu mewakili bit individu serta kelompok bit. Misalnya, elemen sekuensial bit tunggal adalah flip-flop. Namun elemen sekuensial 16-bit adalah register yang dapat menampung 16 bit. Untuk tujuan ini, Verilog memiliki skalar dan vektor jaring dan variabel. Skalar dan Vektor Jaring atau reg d

Verilog

Edge Computing:Apa yang Perlu Diubah untuk Meningkatkan Penggunaannya

Memahami Perbedaan Antara Penggilingan Horizontal dan Vertikal

Menunggu ditahan:bagaimana perasaan konsumen Inggris Raya tentang AI dan chatbots dalam layanan pelanggan

Mengapa Pelatihan Ilmu Material Penting bagi Insinyur Instrumentasi Minyak dan Gas