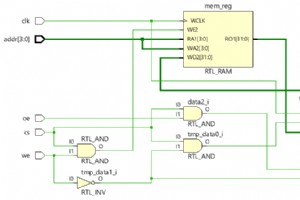

Desain module single_port_sync_ram # (parameter ADDR_WIDTH = 4, parameter DATA_WIDTH = 32, parameter DEPTH = 16 ) ( input clk, input [ADDR_WIDTH-1:0] addr, inout [DATA_WIDTH-1:0] data, input cs, input we, input oe ); re

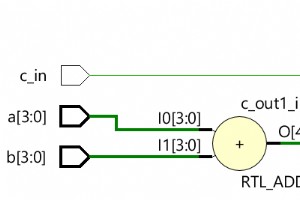

Penjumlah adalah komponen digital yang melakukan penambahan dua angka. Ini adalah komponen utama di dalam ALU prosesor dan digunakan untuk menambah alamat, indeks tabel, pointer buffer, dan di banyak tempat lain di mana penambahan diperlukan. Sebuah penambah penuh menambahkan input carry bersama de

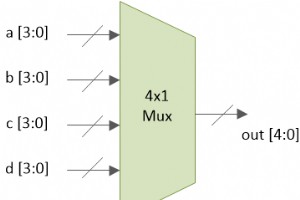

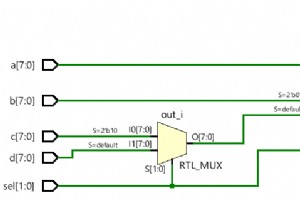

Apa itu mux atau multiplexer? Multiplexer atau mux singkatnya, adalah elemen digital yang mentransfer data dari salah satu input N ke output berdasarkan sinyal pilih. Kasus yang ditunjukkan di bawah ini adalah ketika N sama dengan 4. Misalnya, multiplexer 4 bit akan memiliki N input masing-masing 4

Desain module pr_en ( input [7:0] a, input [7:0] b, input [7:0] c, input [7:0] d, input [1:0] sel, output reg [7:0] out); always @ (a or b or c or d or sel) begin if (sel == 2b00) out <= a; else

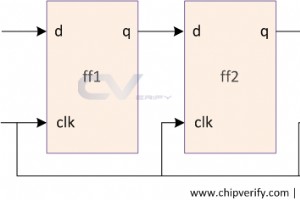

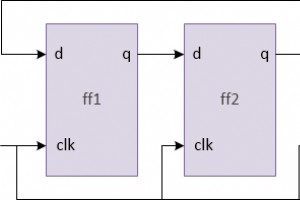

Dalam elektronik digital, register geser adalah kaskade flip-flop di mana pin keluaran q dari satu kegagalan terhubung ke pin input data (d) berikutnya. Karena semua flop bekerja pada jam yang sama, array bit yang disimpan dalam register geser akan bergeser satu posisi. Misalnya, jika register geser

Desain module gray_ctr # (parameter N = 4) ( input clk, input rstn, output reg [N-1:0] out); reg [N-1:0] q; always @ (posedge clk) begin if (!rstn) begin q <= 0; out <= 0; end else begin q <= q + 1; `ifdef FOR_LOOP for (int i

Desain module modN_ctr # (parameter N = 10, parameter WIDTH = 4) ( input clk, input rstn, output reg[WIDTH-1:0] out); always @ (posedge clk) begin if (!rstn) begin out <= 0; end else begin if (out == N-1) out <= 0; else ou

Desain module johnson_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= ~out[0]; for (int i = 0; i < WIDTH-1; i=i+1

Desain module ring_ctr #(parameter WIDTH=4) ( input clk, input rstn, output reg [WIDTH-1:0] out ); always @ (posedge clk) begin if (!rstn) out <= 1; else begin out[WIDTH-1] <= out[0]; for (int i = 0; i < WIDTH-1; i=i+1) b

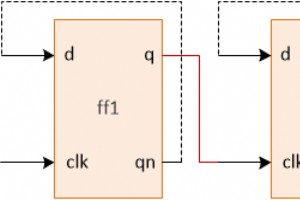

riak pencacah adalah pencacah asinkron di mana semua flop kecuali yang pertama di-clock oleh output dari flop sebelumnya. Desain module dff ( input d, input clk, input rstn, output reg q, output qn); always @ (posedge clk or neg

Penghitung 4-bit mulai bertambah dari 4b0000 ke 4h1111 dan kemudian bergulir kembali ke 4b0000. Ini akan terus menghitung selama dilengkapi dengan jam berjalan dan reset disetel tinggi. Rollover terjadi ketika bit paling signifikan dari penambahan terakhir dibuang. Ketika penghitung berada pada nil

Flip-flop menangkap data pada inputnya di tepi positif atau negatif jam. Hal penting yang perlu diperhatikan adalah bahwa apapun yang terjadi pada data setelah tepi jam sampai tepi jam berikutnya tidak akan tercermin dalam output. Sebuah gerendel di sisi lain, tidak menangkap di tepi jam, sebaliknya

Desain module tff ( input clk, input rstn, input t, output reg q); always @ (posedge clk) begin if (!rstn) q <= 0; else if (t) q <= ~q; else q <= q; end endmodule Testbench module tb; reg clk; reg

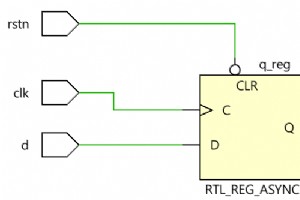

A D flip-flop adalah elemen berurutan yang mengikuti pin input d di tepi jam tertentu. Desain #1:Dengan reset aktif-rendah async module dff ( input d, input rstn, input clk, output reg q); always @ (posedge clk or negedge rstn) if (!rstn)

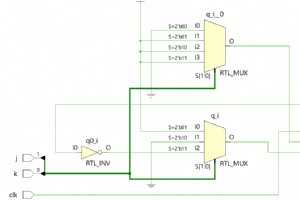

Desain module jk_ff ( input j, input k, input clk, output q); reg q; always @ (posedge clk) case ({j,k}) 2b00 : q <= q; 2b01 : q <= 0; 2b10 : q <= 1; 2b11 : q <= ~q; endcase endmodule Ske

Itu selalu yang terbaik untuk memulai menggunakan contoh yang sangat sederhana, dan tidak ada yang memberikan tujuan terbaik selain Hello World !. // Single line comments start with double forward slash // // Verilog code is always written inside modules, and each module represents a digital bl

Verilog memiliki tugas dan fungsi sistem yang dapat membuka file, mengeluarkan nilai ke dalam file, membaca nilai dari file dan memuat ke variabel lain serta menutup file. Membuka dan menutup file module tb; // Declare a variable to store the file handler integer fd; initial begin // Ope

Skala waktu default Meskipun modul Verilog diharapkan memiliki skala waktu yang ditentukan sebelum modul, simulator dapat memasukkan skala waktu default. Skala waktu aktual yang diterapkan pada cakupan apa pun dalam hierarki yang diuraikan Verilog dapat dicetak menggunakan tugas sistem $printtimesc

Arahan skala waktu Verilog menentukan unit waktu dan presisi untuk simulasi. Verilog $timeformat fungsi sistem menentukan %t gaya pelaporan penentu format dalam pernyataan tampilan seperti $display dan $strobe . Sintaks $timeformat(<unit_number>, <precision>, <suffix_string>,

Fungsi matematika Verilog dapat digunakan sebagai pengganti ekspresi konstan dan mendukung keduanya bilangan bulat dan nyata matematika. Fungsi Matematika Bilangan Bulat Fungsi $clog2 mengembalikan langit-langit log2 dari argumen yang diberikan. Ini biasanya digunakan untuk menghitung lebar minimu

Verilog